ईपीओएन प्रणाली में,ओएलटीएकाधिक से जुड़ा हैजिम्मेदारी(ऑप्टिकल नेटवर्क इकाइयां) एक पीओएस (निष्क्रिय ऑप्टिकल स्प्लिटर) के माध्यम से। EPON के मूल के रूप में,ओएलटीऑप्टिकल मॉड्यूल सीधे पूरे 10G EPON सिस्टम के संचालन को प्रभावित करेंगे।

1. 10G EPON सममित का परिचयओएलटीऑप्टिकल मॉड्यूल

10G EPON सममितओएलटीऑप्टिकल मॉड्यूल अपलिंक बर्स्ट रिसेप्शन और डाउनलिंक निरंतर ट्रांसमिशन मोड का उपयोग करता है, जो मुख्य रूप से 10G EPON सिस्टम में ऑप्टिकल / इलेक्ट्रिकल रूपांतरण के लिए उपयोग किया जाता है।

प्राप्त करने वाले हिस्से में एक टीआईए (ट्रांसिम्पेडेंस एम्पलीफायर), 1270/1310 एनएम पर एक एपीडी (एवलांच फोटोडायोड), और 1.25 और 10.3125 जीबीपीएस दर पर दो एलए (सीमित एम्पलीफायर) शामिल हैं।

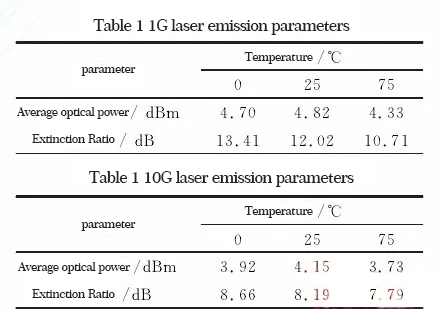

संचारण अंत 10G EML (इलेक्ट्रो-अवशोषण मॉड्यूलेशन लेजर) और 1.25 Gbit/s DFB (वितरित फीडबैक लेजर) से बना है, और इसकी उत्सर्जन तरंग दैर्ध्य क्रमशः 1577 और 1490nm हैं।

ड्राइविंग सर्किट में स्थिर 10G लेजर उत्सर्जन तरंग दैर्ध्य बनाए रखने के लिए एक डिजिटल एपीसी (स्वचालित ऑप्टिकल पावर कंट्रोल) सर्किट और एक टीईसी (तापमान मुआवजा) सर्किट शामिल है। ट्रांसमिटिंग और रिसीविंग पैरामीटर मॉनिटरिंग SFF-8077iv4.5 प्रोटोकॉल के अनुसार सिंगल चिप माइक्रो कंप्यूटर द्वारा कार्यान्वित की जाती है।

क्योंकि का प्राप्त अंतओएलटीऑप्टिकल मॉड्यूल बर्स्ट रिसेप्शन का उपयोग करता है, रिसेप्शन सेटअप समय विशेष रूप से महत्वपूर्ण है। यदि रिसेप्शन को व्यवस्थित करने का समय लंबा है, तो यह संवेदनशीलता को बहुत प्रभावित करेगा, और यहां तक कि बर्स्ट रिसेप्शन ठीक से काम नहीं कर सकता है। IEEE 802.3av प्रोटोकॉल की आवश्यकताओं के अनुसार, 1.25Gbit/s बर्स्ट रिसेप्शन का स्थापना समय <400 ns होना चाहिए, और बर्स्ट रिसेप्शन संवेदनशीलता 10-12 की बिट त्रुटि दर के साथ <-29.78 dBm होनी चाहिए; और 10.3125 Gbit/s बर्स्ट रिसेप्शन सेटअप समय <800ns होना चाहिए, और बर्स्ट रिसेप्शन संवेदनशीलता 10-3 की बिट त्रुटि दर के साथ <-28.0 dBm होनी चाहिए।

2.10G EPON सममितओएलटीऑप्टिकल मॉड्यूल डिजाइन

2.1 डिज़ाइन योजना

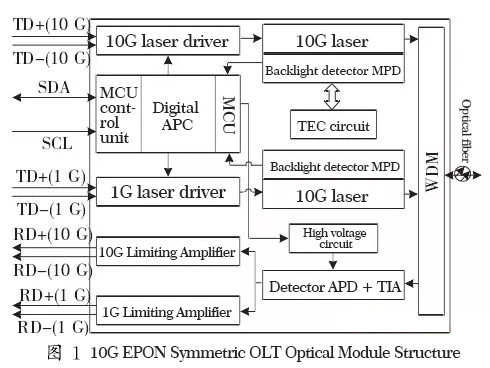

10G EPON सममितओएलटीऑप्टिकल मॉड्यूल एक ट्रिपलएक्सर (सिंगल-फाइबर थ्री-वे मॉड्यूल) से बना है, जो ट्रांसमिटिंग, रिसीविंग और मॉनिटरिंग करता है। ट्रिपलएक्सर में दो लेजर और एक डिटेक्टर शामिल हैं। प्रेषित प्रकाश और प्राप्त प्रकाश को एकल-फाइबर द्विदिशात्मक संचरण प्राप्त करने के लिए WDM (वेवलेंथ डिवीजन मल्टीप्लेक्सर) के माध्यम से ऑप्टिकल डिवाइस में एकीकृत किया जाता है। इसकी संरचना चित्र 1 में दिखाई गई है।

ट्रांसमिटिंग भाग में दो लेज़र होते हैं, जिनका मुख्य कार्य क्रमशः 1G और 10G विद्युत संकेतों को ऑप्टिकल सिग्नल में परिवर्तित करना और एक डिजिटल एपीसी सर्किट के माध्यम से बंद लूप स्थिति में ऑप्टिकल पावर स्थिरता बनाए रखना है। उसी समय, सिंगल-चिप माइक्रो कंप्यूटर सिस्टम द्वारा आवश्यक विलुप्त होने के अनुपात को प्राप्त करने के लिए मॉड्यूलेशन करंट के परिमाण को नियंत्रित करता है। TEC सर्किट को 10G ट्रांसमिटिंग सर्किट में जोड़ा जाता है, जो 10G लेजर के आउटपुट तरंग दैर्ध्य को काफी हद तक स्थिर करता है। प्राप्तकर्ता भाग पता लगाए गए फट ऑप्टिकल सिग्नल को विद्युत सिग्नल में परिवर्तित करने के लिए एपीडी का उपयोग करता है, और प्रवर्धन और आकार देने के बाद इसे आउटपुट करता है। यह सुनिश्चित करने के लिए कि संवेदनशीलता आदर्श सीमा तक पहुंच सके, विभिन्न तापमानों पर एपीडी को एक स्थिर उच्च दबाव प्रदान करना आवश्यक है। एक-चिप कंप्यूटर APD हाई-वोल्टेज सर्किट को नियंत्रित करके इस लक्ष्य को प्राप्त करता है।

2.2 दोहरी दर विस्फोट रिसेप्शन का कार्यान्वयन

10G EPON सममित का प्राप्त भागओएलटीऑप्टिकल मॉड्यूल बर्स्ट रिसीविंग विधि का उपयोग करता है। इसे 1.25 और 10.3125 Gbit/s की दो अलग-अलग दरों के बर्स्ट सिग्नल प्राप्त करने की आवश्यकता होती है, जिसके लिए स्थिर आउटपुट विद्युत संकेतों को प्राप्त करने के लिए प्राप्त करने वाले हिस्से को इन दो अलग-अलग दरों के ऑप्टिकल संकेतों को अच्छी तरह से अलग करने में सक्षम होना आवश्यक है। दोहरे दर विस्फोट रिसेप्शन को लागू करने के लिए दो योजनाएंओएलटीऑप्टिकल मॉड्यूल यहां प्रस्तावित हैं।

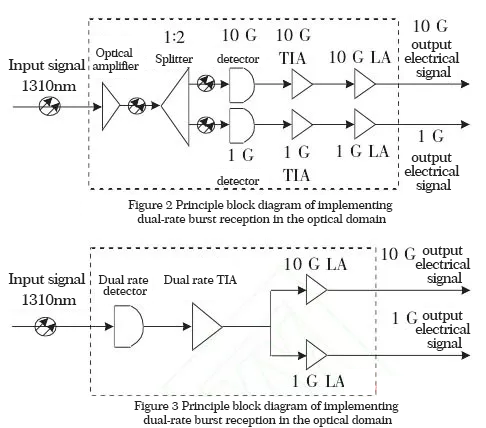

क्योंकि इनपुट ऑप्टिकल सिग्नल टीडीएमए (टाइम डिवीजन मल्टीपल एक्सेस) तकनीक का उपयोग करता है, एक ही समय में विस्फोट प्रकाश की केवल एक दर मौजूद हो सकती है। इनपुट सिग्नल को ऑप्टिकल डोमेन में 1:2 ऑप्टिकल स्प्लिटर के माध्यम से अलग किया जा सकता है, जैसे कि चित्र 2 में दिखाया गया है। या 1G और 10G ऑप्टिकल सिग्नल को कमजोर इलेक्ट्रिकल सिग्नल में बदलने के लिए केवल हाई-स्पीड डिटेक्टर का उपयोग करें, और फिर दो इलेक्ट्रिकल को अलग करें बड़े बैंडविड्थ टीआईए के माध्यम से विभिन्न दरों के साथ सिग्नल, जैसा कि चित्र 3 में दिखाया गया है।

चित्र 2 में दिखाई गई पहली योजना एक निश्चित सम्मिलन हानि लाएगी जब प्रकाश 1: 2 ऑप्टिकल स्प्लिटर से गुज़रता है, जिसे इनपुट ऑप्टिकल सिग्नल को बढ़ाना होगा, इसलिए ऑप्टिकल स्प्लिटर के सामने एक ऑप्टिकल एम्पलीफायर स्थापित किया जाता है। अलग किए गए ऑप्टिकल सिग्नलों को फिर विभिन्न दरों के डिटेक्टरों द्वारा ऑप्टिकल/इलेक्ट्रिकल रूपांतरण के अधीन किया जाता है, और अंत में दो प्रकार के स्थिर विद्युत सिग्नल आउटपुट प्राप्त होते हैं। इस समाधान का सबसे बड़ा नुकसान यह है कि एक ऑप्टिकल एम्पलीफायर और 1: 2 ऑप्टिकल स्प्लिटर का उपयोग किया जाता है, और ऑप्टिकल सिग्नल को परिवर्तित करने के लिए दो डिटेक्टरों की आवश्यकता होती है, जिससे कार्यान्वयन की जटिलता बढ़ जाती है और लागत बढ़ जाती है।

चित्र में दर्शाई गई दूसरी योजना में। 3, विद्युत डोमेन में पृथक्करण प्राप्त करने के लिए इनपुट ऑप्टिकल सिग्नल को केवल एक डिटेक्टर और एक टीआईए से गुजरना पड़ता है। इस समाधान का मूल TIA के चयन में निहित है, जिसके लिए TIA को 1 ~ 10Gbit/s की बैंडविड्थ की आवश्यकता होती है, और साथ ही TIA के पास इस बैंडविड्थ के भीतर तेज़ प्रतिक्रिया होती है। केवल टीआईए के वर्तमान पैरामीटर के माध्यम से प्रतिक्रिया मूल्य जल्दी से प्राप्त किया जा सकता है, प्राप्त संवेदनशीलता की अच्छी तरह से गारंटी दी जा सकती है। यह समाधान कार्यान्वयन की जटिलता को काफी कम कर देता है और लागत को नियंत्रण में रखता है। वास्तविक डिज़ाइन में, हम आम तौर पर दोहरी-दर विस्फोट रिसेप्शन प्राप्त करने के लिए दूसरी योजना चुनते हैं।

2.3 प्राप्त सिरे पर हार्डवेयर सर्किट का डिज़ाइन

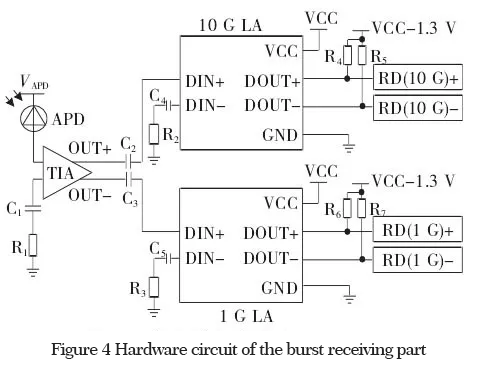

चित्र 4 बर्स्ट प्राप्त करने वाले हिस्से का हार्डवेयर सर्किट है। जब कोई फटा हुआ ऑप्टिकल इनपुट होता है, तो एपीडी ऑप्टिकल सिग्नल को एक कमजोर विद्युत सिग्नल में परिवर्तित करता है और इसे टीआईए को भेजता है। सिग्नल को TIA द्वारा 10G या 1G विद्युत सिग्नल में प्रवर्धित किया जाता है। 10G विद्युत संकेत TIA के सकारात्मक युग्मन के माध्यम से 10G LA में इनपुट होता है, और 1G विद्युत संकेत TIA के नकारात्मक युग्मन के माध्यम से 1G LA में इनपुट होता है। कैपेसिटर C2 और C3 कपलिंग कैपेसिटर हैं जिनका उपयोग 10G और 1G AC-युग्मित आउटपुट प्राप्त करने के लिए किया जाता है। एसी-युग्मित विधि को इसलिए चुना गया क्योंकि यह डीसी-युग्मित विधि की तुलना में सरल है।

हालाँकि, एसी कपलिंग में कैपेसिटर का चार्ज और डिस्चार्ज होता है, और सिग्नल की प्रतिक्रिया गति चार्ज और डिस्चार्ज समय स्थिरांक से प्रभावित होती है, यानी सिग्नल का समय पर जवाब नहीं दिया जा सकता है। यह सुविधा रिसेप्शन निपटान समय की एक निश्चित मात्रा खोने के लिए बाध्य है, इसलिए यह चुनना महत्वपूर्ण है कि एसी युग्मन संधारित्र कितना बड़ा है। यदि एक छोटे युग्मन संधारित्र का चयन किया जाता है, तो निपटान समय को छोटा किया जा सकता है, और सिग्नल को प्रेषित किया जा सकता हैओएनयूप्रत्येक टाइम स्लॉट में रिसेप्शन प्रभाव को प्रभावित किए बिना पूरी तरह से प्राप्त किया जा सकता है क्योंकि रिसेप्शन निपटान का समय बहुत लंबा है और अगले टाइम स्लॉट का आगमन होता है।

हालाँकि, बहुत छोटी क्षमता युग्मन प्रभाव को प्रभावित करेगी और रिसेप्शन की स्थिरता को काफी कम कर देगी। बड़ी कैपेसिटेंस सिस्टम घबराहट को कम कर सकती है और प्राप्त अंत की संवेदनशीलता में सुधार कर सकती है। इसलिए, रिसेप्शन निपटान समय और रिसेप्शन संवेदनशीलता को ध्यान में रखने के लिए, उपयुक्त युग्मन कैपेसिटर सी 2 और सी 3 का चयन करने की आवश्यकता है। इसके अलावा, इनपुट विद्युत सिग्नल की स्थिरता सुनिश्चित करने के लिए, 50Ω के प्रतिरोध के साथ एक युग्मन संधारित्र और एक मिलान अवरोधक एलए के नकारात्मक टर्मिनल से जुड़े होते हैं।

LVPECL (लो वोल्टेज पॉजिटिव एमिटर कपलिंग लॉजिक) सर्किट प्रतिरोधक R4 और R5 (R6 और R7) और 10G (1G) LA द्वारा अंतर सिग्नल आउटपुट के माध्यम से 2.0 V DC वोल्टेज स्रोत से बना है। विद्युत संकेत.

2.4 लॉन्च अनुभाग

10G EPON सममित का संचारण भागओएलटीऑप्टिकल मॉड्यूल को मुख्य रूप से 1.25 और 10G ट्रांसमिटिंग के दो भागों में विभाजित किया गया है, जो क्रमशः 1490 और 1577 एनएम की तरंग दैर्ध्य के साथ डाउनलिंक पर सिग्नल भेजते हैं। उदाहरण के तौर पर 10G ट्रांसमिटिंग पार्ट को लेते हुए, 10G डिफरेंशियल सिग्नल की एक जोड़ी CDR (क्लॉक शेपिंग) चिप में प्रवेश करती है, AC को 10G ड्राइवर चिप से जोड़ा जाता है, और अंत में 10G लेजर में अलग-अलग इनपुट किया जाता है। क्योंकि तापमान परिवर्तन का लेजर उत्सर्जन तरंग दैर्ध्य पर बहुत प्रभाव पड़ेगा, तरंग दैर्ध्य को प्रोटोकॉल द्वारा आवश्यक स्तर तक स्थिर करने के लिए (प्रोटोकॉल को 1575 ~ 1580nm की आवश्यकता होती है), टीईसी सर्किट के कामकाजी वर्तमान को समायोजित करने की आवश्यकता है, इसलिए आउटपुट तरंग दैर्ध्य को अच्छी तरह से नियंत्रित किया जा सकता है।

3. परीक्षण के परिणाम और विश्लेषण

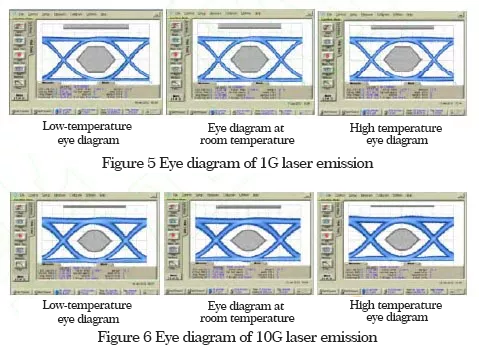

10G EPON सममिति के मुख्य परीक्षण संकेतकओएलटीऑप्टिकल मॉड्यूल में रिसीवर सेटअप समय, रिसीवर संवेदनशीलता और ट्रांसमिट आई आरेख शामिल हैं। विशिष्ट परीक्षण इस प्रकार हैं:

(1) सेटअप समय प्राप्त करें

-24.0 डीबीएम की अपलिंक बर्स्ट ऑप्टिकल पावर के सामान्य कामकाजी वातावरण के तहत, बर्स्ट प्रकाश स्रोत द्वारा उत्सर्जित ऑप्टिकल सिग्नल को माप प्रारंभिक बिंदु के रूप में उपयोग किया जाता है, और मॉड्यूल माप के अंत बिंदु के रूप में एक पूर्ण विद्युत सिग्नल प्राप्त करता है और स्थापित करता है, इसे अनदेखा करता है। परीक्षण फाइबर में प्रकाश की देरी का समय। मापा गया 1जी बर्स्ट रिसेप्शन सेटअप समय 76.7 एनएस है, जो <400 एनएस के अंतरराष्ट्रीय मानक को पूरा करता है; 10G बर्स्ट रिसेप्शन सेटअप समय 241.8 ns है, जो <800 ns के अंतर्राष्ट्रीय मानक को भी पूरा करता है।

3. परीक्षण के परिणाम और विश्लेषण

10G EPON सममिति के मुख्य परीक्षण संकेतकओएलटीऑप्टिकल मॉड्यूल में रिसीवर सेटअप समय, रिसीवर संवेदनशीलता और ट्रांसमिट आई आरेख शामिल हैं। विशिष्ट परीक्षण इस प्रकार हैं:

(1) सेटअप समय प्राप्त करें

-24.0 डीबीएम की अपलिंक बर्स्ट ऑप्टिकल पावर के सामान्य कामकाजी वातावरण के तहत, बर्स्ट प्रकाश स्रोत द्वारा उत्सर्जित ऑप्टिकल सिग्नल को माप प्रारंभिक बिंदु के रूप में उपयोग किया जाता है, और मॉड्यूल माप के अंत बिंदु के रूप में एक पूर्ण विद्युत सिग्नल प्राप्त करता है और स्थापित करता है, इसे अनदेखा करता है। परीक्षण फाइबर में प्रकाश की देरी का समय। मापा गया 1जी बर्स्ट रिसेप्शन सेटअप समय 76.7 एनएस है, जो <400 एनएस के अंतरराष्ट्रीय मानक को पूरा करता है; 10G बर्स्ट रिसेप्शन सेटअप समय 241.8 ns है, जो <800 ns के अंतर्राष्ट्रीय मानक को भी पूरा करता है।