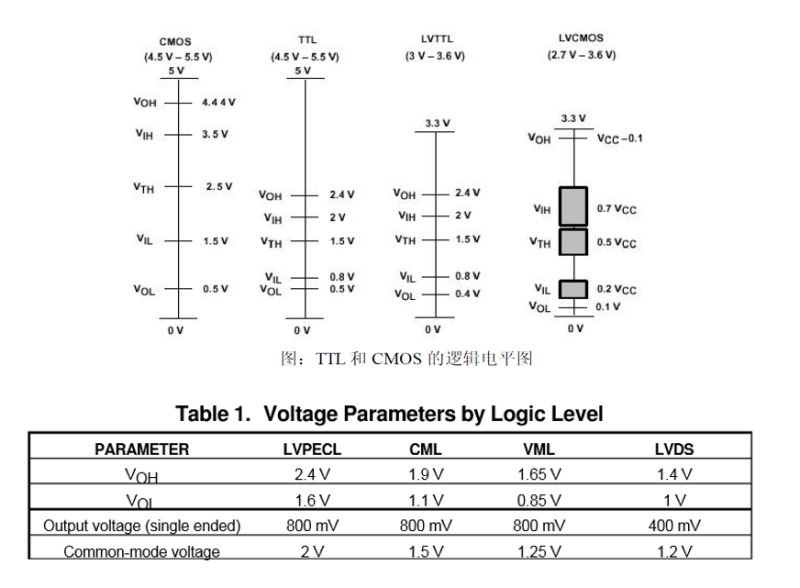

מאמר זה מציג בעיקר את תקני רמת הלוגיקה הנפוצים, כגון CMOS, LVCMOS, TTL, LVTTL, LVDS, PECL / LVPECL, CML, VML, HSTL, SSTL וכו'.

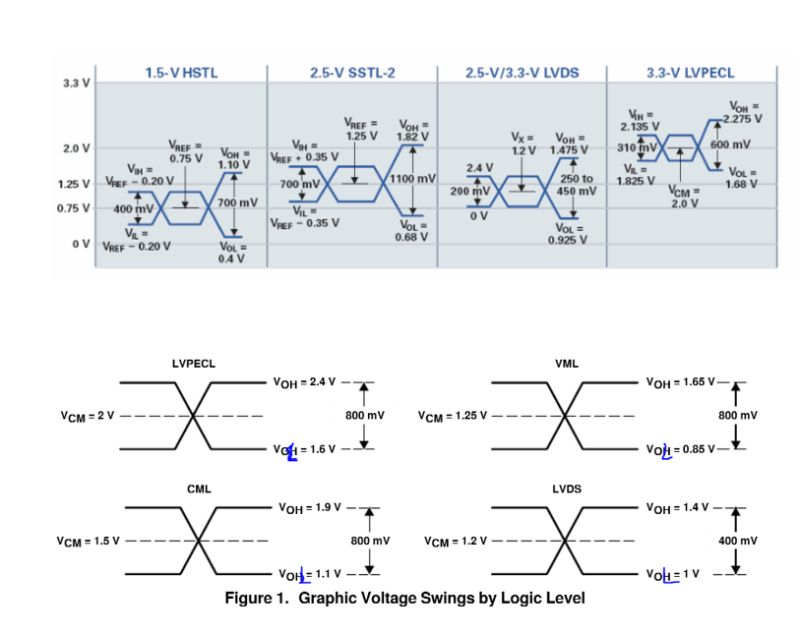

LVPECL:

התעריף הגבוה ביותר: LVPECL הוא 10 + Gbps

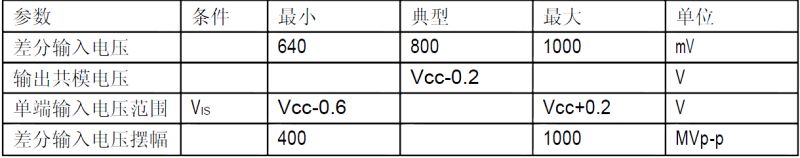

CML:

קצב מקסימלי: 10 + Gbps

מצב צימוד: צימוד Dc משמש בין CML ל-CML כאשר ה-VCC זהה, וצימוד AC משמש בין CML ל-CML כאשר ה-VCC שונה

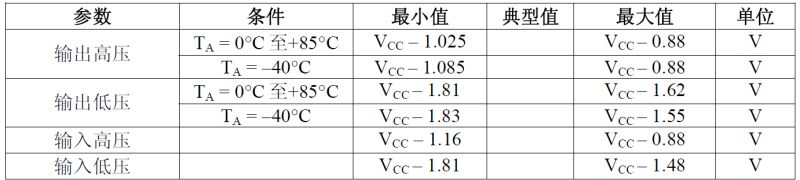

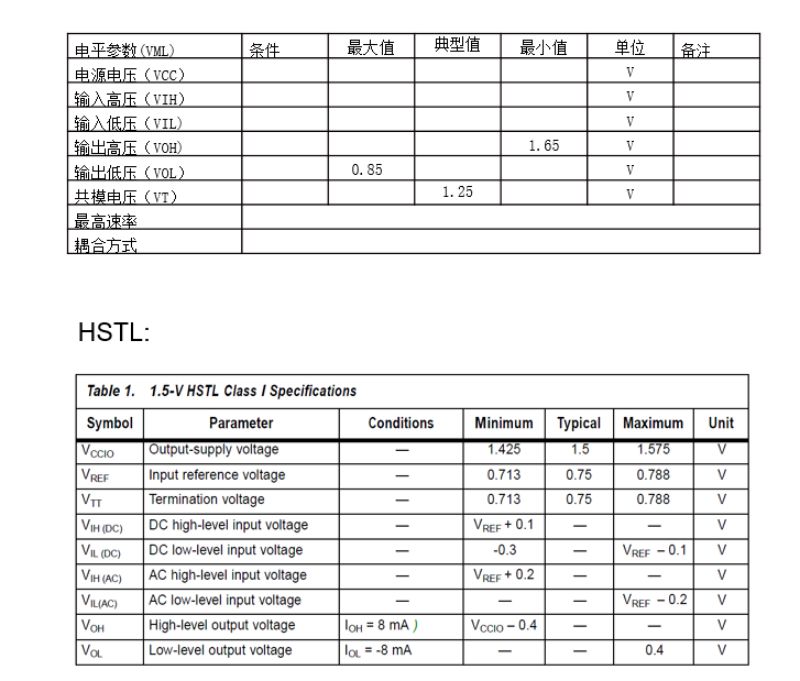

רמת חשמל SSTL

התקן מיועד במיוחד לממשקי זיכרון מהירים (במיוחד SDRAM), הפועלים במהירות של עד 200 מגה-הרץ, ו-SSTL משמש בעיקר בזיכרון DDR. והזהה כמו HSTL. V¬¬CCIO=2.5V, הקלט הוא מבנה השוואה עם רמת ייחוס של 1.25V בקצה אחד ואות כניסה בקצה השני. דרישות רמת הייחוס גבוהות יחסית (דיוק של 1%), HSTL ו-SSTL משמשים לרוב מתחת ל-300M.

האמור לעיל הוא ההקדמה של תקני רמת היגיון נפוצים שהובאו על ידי Shenzhen HDV Phoelectron Technology Co., LTD. סדרת המודולים האופטיים הקשורים לנו כוללת: מודול אופטי SFP, מודול אופטי SFF, מודול אופטי תקשורת, מודול אופטי 1x9, מודול אופטי ציוד תקשורת, מודול אופטי דו-כיווני סיבים כפולים וכן הלאה. אם יש לך סוגים נוספים של דרישות מודול, נא להתייעץ עוד.