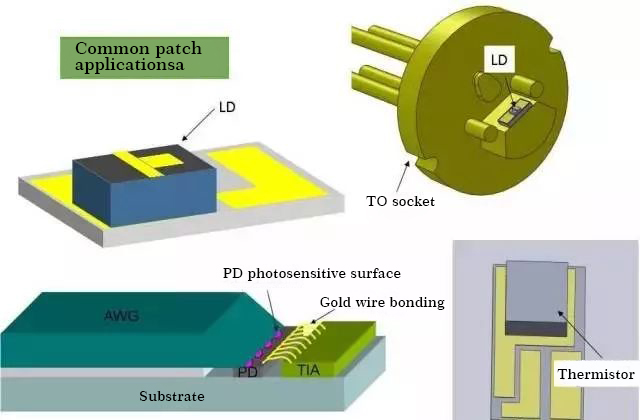

チップを受け取るプロセスの最初のステップはパッチです。 TO には、TO ソケットにヒートシンクするパッチ、ヒートシンクに LD するチップ、およびバックライト PD が含まれます。

具体的な実装プロセスは大きく異なる場合があります。通常、取り付けられる対象物は LD / PD チップ、または TIA、抵抗 / コンデンサです。配置は窒化アルミニウムのヒートシンク上で、または PCB 上で直接実行できます。配置には共晶溶接または導電性接着剤を使用できます。パッチには、TIA、抵抗器、パッシブ フリップチップ溶接などのサブミクロンの精度など、数十、さらには数百ミクロンの精度しか必要ありません。

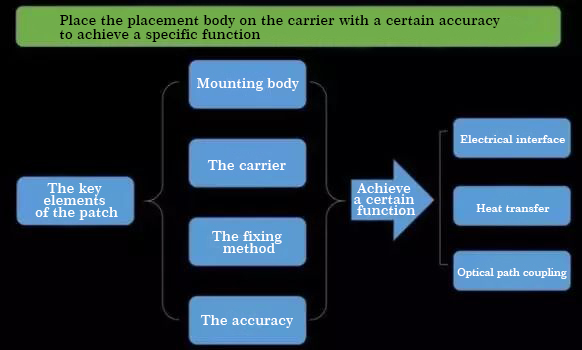

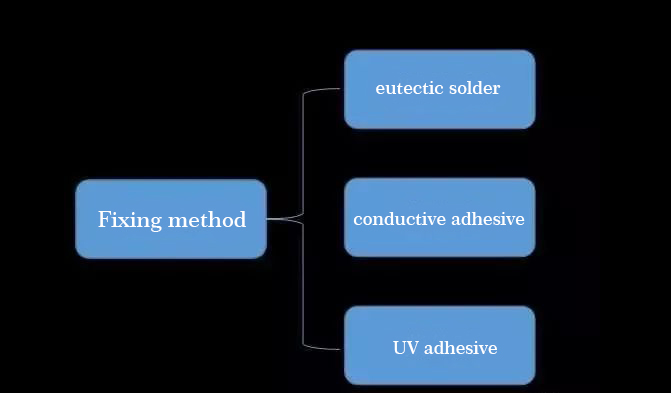

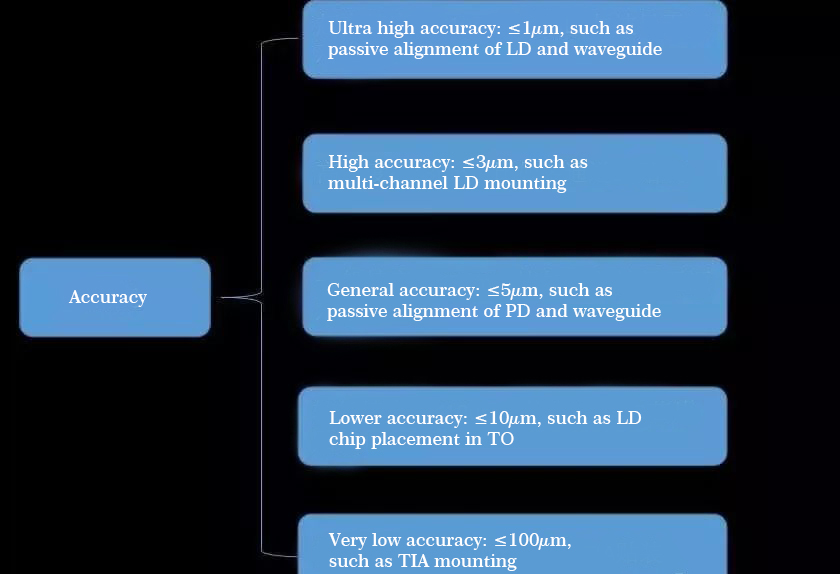

ここまで述べてきましたが、パッチとは一体何でしょうか?標準化された定義は決してないようです。しかし、上記の例からわかるように、装置は特定の機能を達成するために載置体を担体上に一定の精度で載置・固定するために使用されるという共通点がある。 (なぜ装置を使うのか?自動化できる配置プロセスをパッチと呼び、それ以外の場合は手動ボンディングとしか言えないと思います。) この共通点に基づいて、パッチの4つの重要な要素をまとめました。キャリア、固定方式、精度。また、どのようなキャリアが使用されるか、どのようなはんだが選択されるか、どのような精度が要求されるかは、実装される対象物が達成する必要がある機能に完全に依存します。

ここでは、パッチの 4 つの要素に含まれるさまざまな可能性を見ていきます。

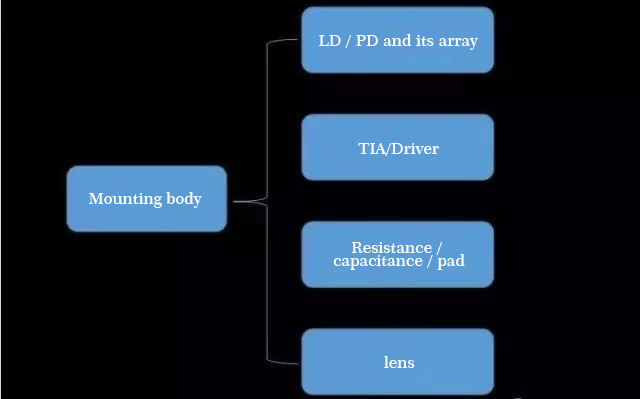

ほとんどのマウントは LD および PD チップです。

TIA/ドライバー/抵抗器/コンデンサーなど、高精度を必要としない配置体は、大量ではなく手動交換が可能です。

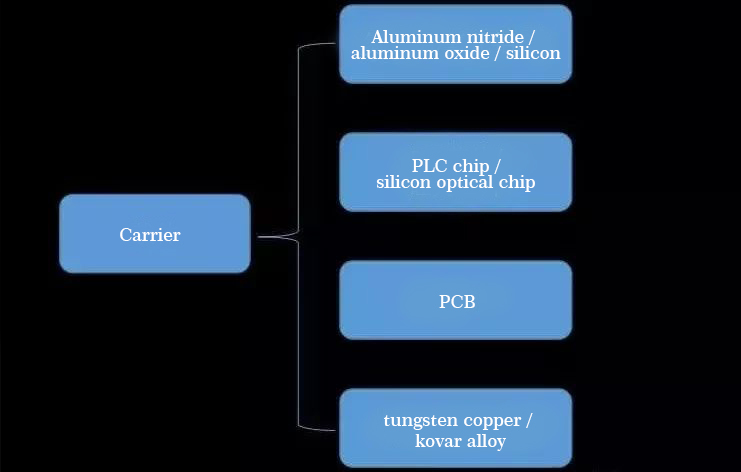

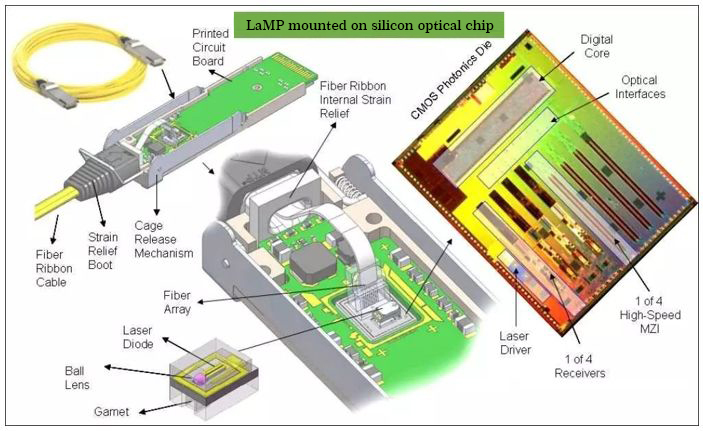

最も伝統的なキャリアは AIN ヒートシンクです。集積チップの発展に伴い、PLCチップやシリコン光チップも一般的な実装体になりました。たとえば、シリコン光格子結合チップなど、シリコン光チップ上にLaMPを実装する必要があります。 PCB は、データ通信 100G-SR4 モジュール、PD / VSCEL などの COB パッケージのコモンキャリアを PCB に直接実装します。

Au80Sn20 合金は、LD マウントの一般的な共晶はんだです。 PDの実装には導電性接着剤がよく使われます。 UV接着固定レンズの方が適しています。

精度は特定のアプリケーションによって異なります。

光路結合が必要な場合、要求される精度は比較的高くなります。

パッシブアライメントには、アクティブカップリングよりも高い精度が必要です。

LDの配置はPDの配置に比べて高い精度が要求されますが、

TIA/抵抗/コンデンサは精度を必要とせず、ただ貼り付けるだけです。

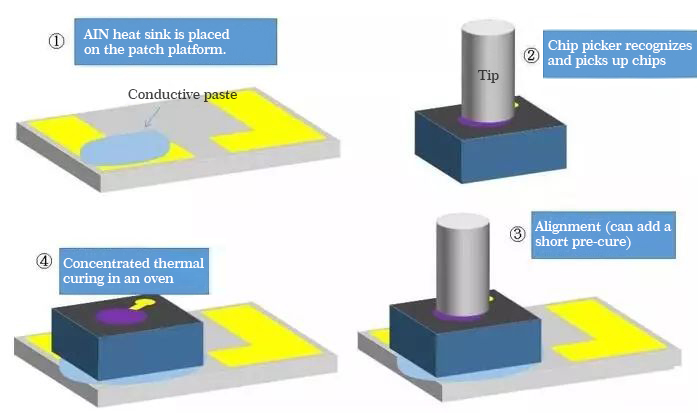

一般的な配置プロセス

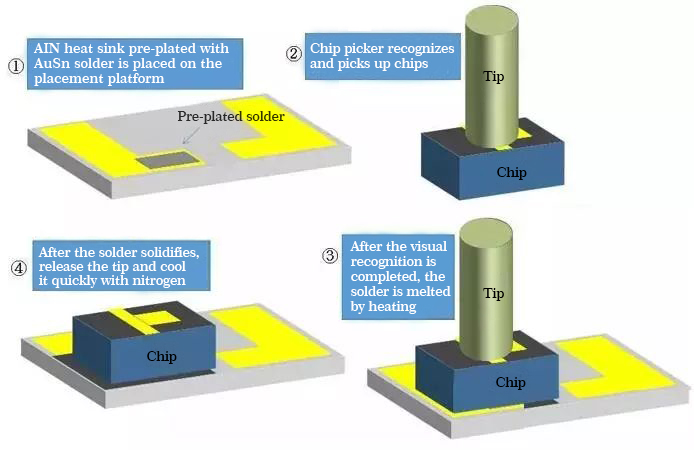

金錫共晶はんだパッチ

導電性ペーストパッチ

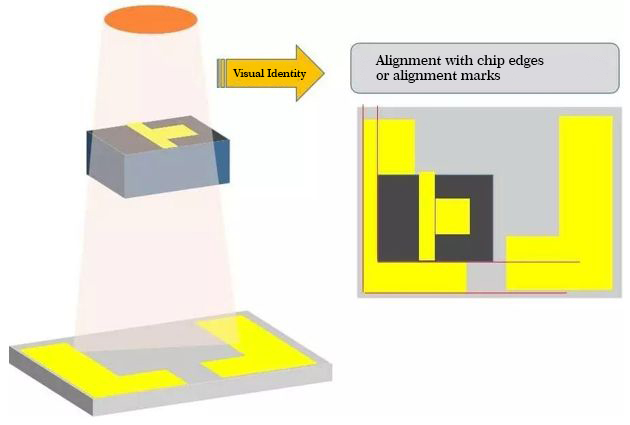

精度が高くない場合は、CCD を見下ろしてチップと基板の画像を同時にキャプチャし、アライメント マークまたはチップ エッジを使用して位置合わせするだけで済みます。

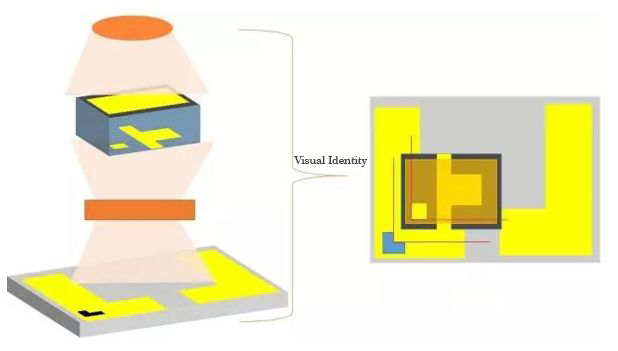

フリップチップ アプリケーションの場合は、チップの底部と基板の表面の両方を監視する複数の CCD も必要です。高精度のアプリケーションには、特別な位置合わせマークも必要です。