Am EPON System ass denOLTass mat Multiple verbonnenONUs(optesch Netzwierk Eenheeten) duerch e POS (passiv opteschen Splitter). Als Kär vun EPON,OLToptesch Moduler beaflossen direkt d'Operatioun vum ganzen 10G EPON System.

1.Aféierung an 10G EPON symmetreschOLTopteschen Modul

Den 10G EPON symmetreschOLTopteschen Modul benotzt den Uplink Burst Empfang an Downlink kontinuéierlech Iwwerdroungsmodi, déi haaptsächlech fir optesch / elektresch Konversioun an 10G EPON Systemer benotzt ginn.

Den Empfangsdeel besteet aus engem TIA (Transimpedanzverstärker), enger APD (Avalanche Photodiode) bei 1270 / 1310nm, an zwee LA (limitéiert Verstärker) bei 1,25 an 10,3125 Gbit / s Tariffer.

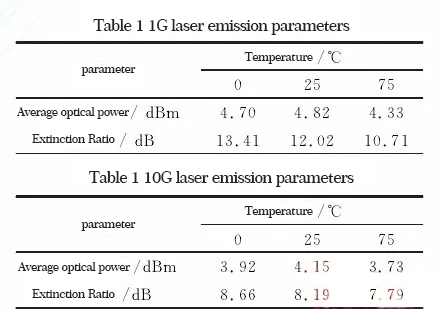

D'Sendende Enn besteet aus engem 10G EML (Elektro-Absorptiounsmodulatiounslaser) an engem 1,25 Gbit / s DFB (verdeelt Feedback Laser), a seng Emissiounswellelängten sinn 1577 respektiv 1490nm.

De dreiwend Circuit enthält en digitalen APC (Automatic Optical Power Control) Circuit an en TEC (Temperature Compensation) Circuit fir eng stabil 10G Laser Emissioun Wellelängt z'erhalen. D'Sendung an d'Empfangsparameter Iwwerwaachung gëtt vum Single Chip Mikrocomputer no dem SFF-8077iv4.5 Protokoll ëmgesat.

Well de Empfang vun derOLTopteschen Modul benotzt Burst Empfang, d'Empfangssetupzäit ass besonnesch wichteg. Wann d'Receptiounszäit laang ass, wäert et d'Sensibilitéit staark beaflossen, a ka souguer verursaachen datt de Burstempfang net richteg funktionnéiert. No den Ufuerderunge vum IEEE 802.3av Protokoll muss d'Etablissementszäit vun engem 1.25Gbit / s Burstempfang <400 ns sinn, an d'Sensibilitéit fir Burstempfang muss <-29.78 dBm mat engem Bitfehlerquote vun 10-12 sinn; an 10,3125 Gbit / s D'Burst Empfang Setup Zäit muss <800ns sinn, an der Burst Empfangsempfindlechkeet muss <-28,0 dBm sinn mat engem Bitfehlerquote vun 10-3.

2.10G EPON symmetreschOLTopteschen Modul Design

2.1 Design Schema

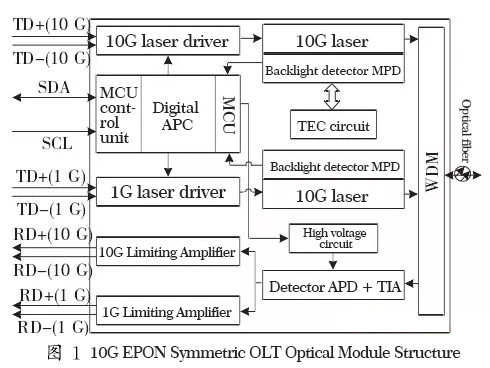

Den 10G EPON symmetreschOLTopteschen Modul besteet aus engem Triplexer (Eenfaser Dräi-Wee Modul), Iwwerdroung, Empfang an Iwwerwaachung. Den Triplexer enthält zwee Laser an en Detektor. D'transmittéiert Liicht an d'empfangent Liicht ginn an den opteschen Apparat duerch WDM (Wavelength Division Multiplexer) integréiert fir Single-Fiber Bidirectional Transmissioun z'erreechen. Seng Struktur ass an der Figur 1 gewisen.

D'Sendungsdeel besteet aus zwee Laser, deenen hir Haaptfunktioun ass, 1G an 10G elektresch Signaler an optesch Signaler ze konvertéieren, respektiv, an d'optesch Kraaftstabilitéit an engem zouene Schleifenzoustand duerch en digitale APC Circuit z'erhalen. Zur selwechter Zäit kontrolléiert de Single-Chip Mikrocomputer d'Gréisst vum Modulatiounsstroum fir den Ausstierwensverhältnis ze kréien, deen vum System erfuerderlech ass. Den TEC Circuit gëtt zum 10G Senderkrees bäigefüügt, wat d'Ausgangswellelängt vum 10G Laser staark stabiliséiert. Den Empfangsdeel benotzt APD fir dat detektéierten Burst opteschen Signal an en elektrescht Signal ze konvertéieren, a gëtt et no Verstäerkung a Formen eraus. Fir sécherzestellen datt d'Sensibilitéit den ideale Beräich erreechen kann, ass et néideg fir e stabilen Héichdrock op d'APD bei verschiddenen Temperaturen ze bidden. Den One-Chip Computer erreecht dëst Zil andeems Dir den APD Héichspannungskrees kontrolléiert.

2.2 Ëmsetzung vun Dual-Taux Burst Empfang

De Empfangsdeel vum 10G EPON symmetrescheOLTopteschen Modul benotzt eng Burst Empfangsmethod. Et muss Burst-Signaler vun zwee verschiddenen Tariffer vun 1,25 an 10,3125 Gbit / s kréien, wat den Empfangsdeel erfuerdert fir d'optesch Signaler vun dësen zwou verschiddenen Tariffer gutt z'ënnerscheeden fir stabil Ausgab elektresch Signaler ze kréien. Zwee Scheme fir Ëmsetzung vun duebel-Taux Burst Empfang vunOLToptesch Moduler ginn hei proposéiert.

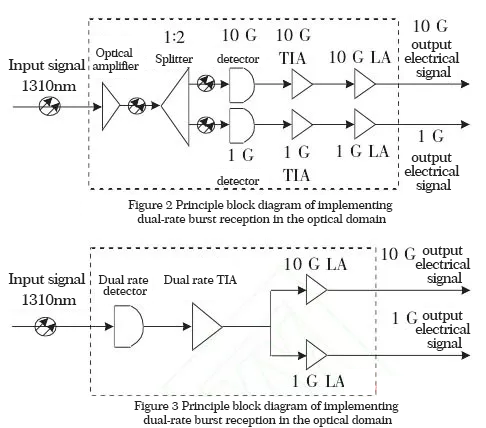

Well den opteschen Input Signal TDMA (Time Division Multiple Access) Technologie benotzt, kann nëmmen een Taux vu Burstlicht zur selwechter Zäit existéieren. D'Input Signal kann am opteschen Domain duerch en 1: 2 opteschen Splitter getrennt ginn, wéi an der Figur 2. Oder benotzt nëmmen e High-Speed-Detektor fir 1G an 10G optesch Signaler a schwaach elektresch Signaler ze konvertéieren an dann zwee elektresch ze trennen. Signaler mat verschiddene Tariffer duerch eng méi grouss Bandbreed TIA, wéi an der Figur 3.

Den éischte Schema, deen an der Figur 2 ugewise gëtt, bréngt e gewëssen Insertiounsverloscht wann d'Liicht duerch den 1: 2 opteschen Splitter passéiert, deen den opteschen Input Signal verstäerken muss, sou datt en opteschen Verstärker virum opteschen Splitter installéiert ass. Déi getrennt optesch Signaler ginn dann optesch / elektresch Konversioun duerch Detektore vu verschiddene Tariffer ënnerworf, a schliisslech ginn zwou Aarte vu stabile elektresche Signalausgaben kritt. De gréissten Nodeel vun dëser Léisung ass datt en opteschen Verstärker an en 1: 2 opteschen Splitter benotzt ginn, an zwee Detektoren sinn néideg fir den opteschen Signal ze konvertéieren, wat d'Komplexitéit vun der Ëmsetzung erhéicht an d'Käschte erhéicht.

Am zweete Schema an Fig. 3, muss den opteschen Input Signal nëmmen duerch en Detektor an en TIA passéieren fir Trennung am elektresche Domain z'erreechen. De Kär vun dëser Léisung läit an der Auswiel vun TIA, déi TIA erfuerdert eng Bandbreedung vun 1 ~ 10Gbit / s ze hunn, a gläichzäiteg huet TIA séier Äntwert bannent dëser Bandbreedung. Nëmmen duerch den aktuellen Parameter vun TIA kann den Äntwertwäert séier kréien, d'Empfangsempfindlechkeet ka gutt garantéiert ginn. Dës Léisung reduzéiert immens d'Komplexitéit vun der Ëmsetzung an hält d'Käschte ënner Kontroll. Am eigentlechen Design wielen mir allgemeng den zweete Schema fir Dual-Rate Burst Empfang z'erreechen.

2.3 Design vun der Hardware Circuit um Empfang

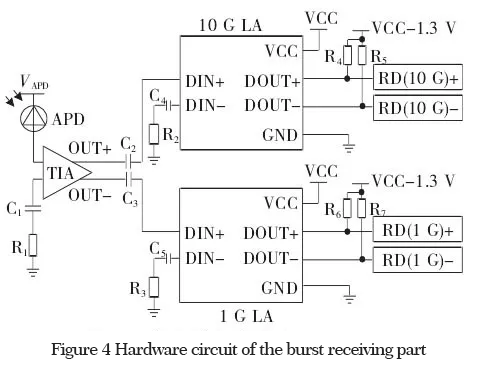

Fig. 4 ass den Hardware Circuit vum Burst Empfangsdeel. Wann et e burst opteschen Input gëtt, konvertéiert d'APD den opteschen Signal an e schwaacht elektrescht Signal a schéckt et un d'TIA. D'Signal gëtt vun der TIA an en 10G oder 1G elektrescht Signal verstäerkt. Den 10G elektresche Signal gëtt an den 10G LA duerch déi positiv Kupplung vun der TIA Input, an den 1G elektresche Signal gëtt an den 1G LA duerch déi negativ Kupplung vun der TIA Input. Kondensatoren C2 an C3 sinn Kupplungskondensatoren déi benotzt gi fir 10G an 1G AC-gekoppelter Output z'erreechen. D'AC-gekoppelte Method gouf gewielt well se méi einfach ass wéi d'DC-gekoppelte Method.

Wéi och ëmmer, d'AC-Kupplung huet d'Laascht an d'Entladung vum Kondensator, an d'Äntwertgeschwindegkeet op d'Signal gëtt vun der Ladungs- an Entladungszäitkonstant beaflosst, dat heescht, d'Signal kann net an der Zäit geäntwert ginn. Dës Fonktioun ass gebonnen fir e gewësse Betrag vun der Empfangssettungszäit ze verléieren, also ass et wichteg ze wielen wéi grouss den AC Kupplungskondensator ass. Wann e méi klenge Kupplungskondensator ausgewielt gëtt, kann d'Settlementzäit verkierzt ginn, an d'Signal iwwerdroe vumONUan all Zäit Stonneplang kann komplett empfaangen ouni Afloss op d'Empfang Effekt well d'Receptioun Settlement Zäit ze laang ass an d'Arrivée vun der nächster Zäit Stonneplang.

Wéi och ëmmer, ze kleng Kapazitéit wäert de Kupplungseffekt beaflossen an d'Stabilitéit vum Empfang staark reduzéieren. Méi grouss Kapazitéit kann System Jitter reduzéieren an d'Sensibilitéit vum Empfangsend verbesseren. Dofir, fir d'Receptiounssëtzungszäit an d'Empfangsempfindlechkeet ze berücksichtegen, mussen déi entspriechend Kupplungskondensatoren C2 an C3 ausgewielt ginn. Zousätzlech, fir d'Stabilitéit vum elektresche Input Signal ze garantéieren, sinn e Kupplungskondensator an e passende Widderstand mat enger Resistenz vu 50Ω un den negativen Terminal vun LA verbonnen.

LVPECL (Low Voltage Positive Emitter Coupling Logic) Circuit besteet aus Widderstänn R4 an R5 (R6 an R7) an enger 2,0 V DC Spannungsquell duerch d'Differentialsignalausgang vun 10G (1G) LA. elektrescht Signal.

2.4 Start Rubrik

De übertragende Deel vum 10G EPON symmetrescheOLTopteschen Modul ass haaptsächlech opgedeelt an zwee Deeler vun 1.25 an 10G Iwwerdroung, déi respektiv Signaler mat enger Wellelängt vun 1490 an 1577 nm un den Downlink schécken. Huelt den 10G Iwwerdroungsdeel als Beispill, e Paar 10G Differentialsignaler erakommen an en CDR (Clock Shaping) Chip, ass AC-gekoppelt mat engem 10G Driver Chip, a schlussendlech gëtt differenziell an en 10G Laser input. Well d'Temperaturännerung e groussen Afloss op d'Laser-Emissiounswellelängt huet, fir d'Wellenlängt op den Niveau ze stabiliséieren, dee vum Protokoll erfuerderlech ass (de Protokoll erfuerdert 1575 ~ 1580nm), muss den Aarbechtsstroum vum TEC Circuit ugepasst ginn, also datt d'Ausgangswellelängt gutt kontrolléiert ka ginn.

3. Test Resultater an Analyse

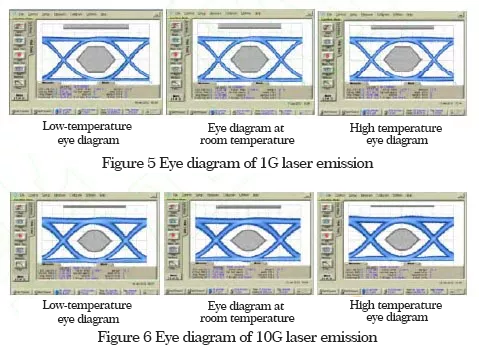

D'Haapttest Indikatoren vun der 10G EPON symmetreschOLTopteschen Modul enthalen d'Empfängersetupzäit, d'Empfängerempfindlechkeet, an d'Aendiagramm iwwerdroen. Déi spezifesch Tester sinn wéi follegt:

(1) Kritt Setup Zäit

Ënnert dem normalen Aarbechtsëmfeld vun der Uplink Burst optesch Kraaft vun -24,0 dBm, gëtt den opteschen Signal, deen vun der Burst Liichtquell emittéiert gëtt als Messstartpunkt benotzt, an de Modul kritt an etabléiert e komplett elektrescht Signal als Messendpunkt, ignoréiert de Zäitverzögerung vum Liicht an der Testfaser.Déi gemoossene 1G Burst Empfangszäit ass 76,7 ns, wat dem internationale Standard vu <400 ns entsprécht; d'10G Burst Empfang Setup Zäit ass 241,8 ns, wat och den internationale Standard vun <800 ns entsprécht.

3. Test Resultater an Analyse

D'Haapttest Indikatoren vun der 10G EPON symmetreschOLTopteschen Modul enthalen d'Empfängersetupzäit, d'Empfängerempfindlechkeet, an d'Aendiagramm iwwerdroen. Déi spezifesch Tester sinn wéi follegt:

(1) Kritt Setup Zäit

Ënnert dem normalen Aarbechtsëmfeld vun der Uplink Burst optesch Kraaft vun -24,0 dBm, gëtt den opteschen Signal, deen vun der Burst Liichtquell emittéiert gëtt als Messstartpunkt benotzt, an de Modul kritt an etabléiert e komplett elektrescht Signal als Messendpunkt, ignoréiert de Zäitverzögerung vum Liicht an der Testfaser. Déi gemoossene 1G Burst Empfang Setup Zäit ass 76.7 ns, wat den internationale Standard vun <400 ns entsprécht; d'10G Burst Empfang Setup Zäit ass 241,8 ns, wat och den internationale Standard vun <800 ns entsprécht.