EPON प्रणालीमा, दओएलटीधेरैसँग जोडिएको छONUs(अप्टिकल नेटवर्क एकाइहरू) POS (निष्क्रिय अप्टिकल स्प्लिटर) मार्फत। EPON को मूल रूपमा,ओएलटीअप्टिकल मोड्युलहरूले सम्पूर्ण 10G EPON प्रणालीको सञ्चालनलाई प्रत्यक्ष असर गर्नेछ।

10G EPON सममितको परिचयओएलटीअप्टिकल मोड्युल

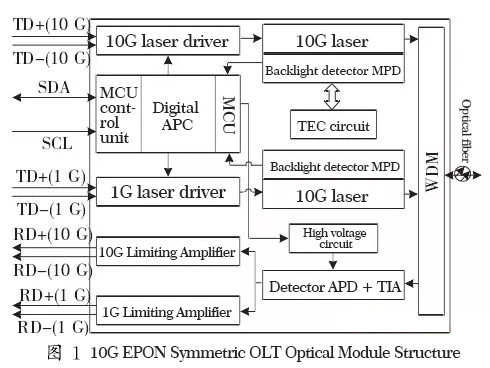

10G EPON सममितओएलटीअप्टिकल मोड्युलले अपलिंक बर्स्ट रिसेप्शन र डाउनलिंक निरन्तर प्रसारण मोडहरू प्रयोग गर्दछ, जुन मुख्य रूपमा 10G EPON प्रणालीहरूमा अप्टिकल / इलेक्ट्रिकल रूपान्तरणको लागि प्रयोग गरिन्छ।

प्राप्त भागमा 1.25 र 10.3125 Gbit / s दरहरूमा एक TIA (ट्रान्सिमपिडेन्स एम्पलीफायर), 1270 / 1310nm मा एक APD (Avalanche Photodiode), र दुई LA (सीमित एम्पलीफायरहरू) समावेश छन्।

प्रसारण अन्त 10G EML (इलेक्ट्रो-अवशोषण मोडुलेशन लेजर) र 1.25 Gbit / s DFB (वितरित प्रतिक्रिया लेजर) बाट बनेको छ, र यसको उत्सर्जन तरंगदैर्ध्य क्रमशः 1577 र 1490nm छन्।

ड्राइभिङ सर्किटमा एक स्थिर 10G लेजर उत्सर्जन तरंगदैर्ध्य कायम राख्नको लागि डिजिटल APC (स्वचालित अप्टिकल पावर कन्ट्रोल) सर्किट र TEC (तापमान क्षतिपूर्ति) सर्किट समावेश छ। प्रसारण र प्राप्त प्यारामिटर निगरानी SFF-8077iv4.5 प्रोटोकल अनुसार एकल चिप माइक्रो कम्प्युटर द्वारा लागू गरिएको छ।

किनभने प्राप्तिको अन्त्य हुन्छओएलटीअप्टिकल मोड्युलले बर्स्ट रिसेप्शन प्रयोग गर्दछ, रिसेप्शन सेटअप समय विशेष गरी महत्त्वपूर्ण छ। यदि रिसेप्शन सेटलिङ समय लामो छ भने, यसले संवेदनशीलतालाई धेरै असर गर्छ, र फट रिसेप्शनले राम्रोसँग काम नगर्न पनि सक्छ। IEEE 802.3av प्रोटोकलका आवश्यकताहरू अनुसार, 1.25Gbit / s बर्स्ट रिसेप्शनको स्थापना समय <400 ns हुनुपर्छ, र बर्स्ट रिसेप्शन संवेदनशीलता 10-12 को बिट त्रुटि दर संग <-29.78 dBm हुनुपर्छ; र 10.3125 Gbit/s बर्स्ट रिसेप्शन सेटअप समय <800ns हुनुपर्छ, र बर्स्ट रिसेप्शन संवेदनशीलता 10-3 को बिट त्रुटि दर संग <-28.0 dBm हुनुपर्छ।

2.10G EPON सममितओएलटीअप्टिकल मोड्युल डिजाइन

2.1 डिजाइन योजना

10G EPON सममितओएलटीअप्टिकल मोड्युल ट्रिपलक्सर (एकल-फाइबर थ्री-वे मोड्युल), ट्रान्समिटिङ, रिसिभिङ र निगरानीबाट बनेको हुन्छ। Triplexer मा दुई लेजर र एक डिटेक्टर समावेश छ। प्रसारित प्रकाश र प्राप्त प्रकाश एकल-फाइबर द्विदिश प्रसारण प्राप्त गर्न WDM (वेभलेन्थ डिभिजन मल्टिप्लेक्सर) मार्फत अप्टिकल उपकरणमा एकीकृत गरिन्छ। यसको संरचना चित्र 1 मा देखाइएको छ।

प्रसारण भागमा दुई लेजरहरू हुन्छन्, जसको मुख्य कार्य क्रमशः 1G र 10G विद्युतीय संकेतहरूलाई अप्टिकल सिग्नलहरूमा रूपान्तरण गर्ने र डिजिटल APC सर्किट मार्फत बन्द लूप अवस्थामा अप्टिकल पावर स्थिरता कायम राख्ने हो। एकै समयमा, एकल-चिप माइक्रो कम्प्युटरले प्रणाली द्वारा आवश्यक विलुप्त अनुपात प्राप्त गर्न मोड्युलेसन वर्तमानको परिमाण नियन्त्रण गर्दछ। TEC सर्किट 10G प्रसारण सर्किटमा थपिएको छ, जसले 10G लेजरको आउटपुट तरंगदैर्ध्यलाई धेरै स्थिर बनाउँछ। प्राप्त भागले पत्ता लगाइएको फट अप्टिकल सिग्नललाई विद्युतीय संकेतमा रूपान्तरण गर्न APD प्रयोग गर्दछ, र प्रवर्धन र आकार पछि यसलाई आउटपुट गर्दछ। संवेदनशीलता आदर्श दायरामा पुग्न सक्छ भन्ने सुनिश्चित गर्न, विभिन्न तापमानहरूमा APD लाई स्थिर उच्च दबाव प्रदान गर्न आवश्यक छ। एक-चिप कम्प्युटरले APD उच्च भोल्टेज सर्किट नियन्त्रण गरेर यो लक्ष्य हासिल गर्दछ।

2.2 दोहोरो-दर बर्स्ट रिसेप्शन को कार्यान्वयन

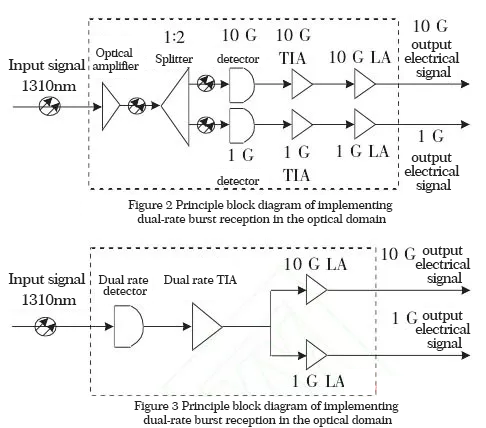

10G EPON सिमेट्रिक को प्राप्त भागओएलटीअप्टिकल मोड्युलले बर्स्ट प्राप्त गर्ने विधि प्रयोग गर्दछ। यसले 1.25 र 10.3125 Gbit / s को दुई फरक दरहरूको फट संकेतहरू प्राप्त गर्न आवश्यक छ, जसलाई प्राप्त गर्ने भागले स्थिर उत्पादन विद्युतीय संकेतहरू प्राप्त गर्न यी दुई फरक दरहरूको अप्टिकल संकेतहरू राम्रोसँग छुट्याउन सक्षम हुन आवश्यक छ। को दोहोरो दर फट स्वागत को लागी दुई योजनाहरुओएलटीअप्टिकल मोड्युलहरू यहाँ प्रस्तावित छन्।

किनभने इनपुट अप्टिकल सिग्नलले TDMA (टाइम डिभिजन मल्टिपल एक्सेस) प्रविधि प्रयोग गर्दछ, एकै समयमा फट प्रकाशको मात्र एक दर अवस्थित हुन सक्छ। इनपुट सिग्नललाई १:२ अप्टिकल स्प्लिटर मार्फत अप्टिकल डोमेनमा अलग गर्न सकिन्छ, जस्तै चित्र २ मा देखाइएको छ। वा 1G र 10G अप्टिकल संकेतहरूलाई कमजोर विद्युतीय संकेतहरूमा रूपान्तरण गर्न उच्च-गति डिटेक्टर मात्र प्रयोग गर्नुहोस्, र त्यसपछि दुईवटा विद्युतीय संकेतहरू अलग गर्नुहोस्। चित्र 3 मा देखाइए अनुसार ठूलो ब्यान्डविथ TIA मार्फत विभिन्न दरहरूसँग सङ्केतहरू।

चित्र 2 मा देखाइएको पहिलो योजनाले 1: 2 अप्टिकल स्प्लिटर मार्फत प्रकाश पार गर्दा एक निश्चित प्रविष्टि हानि ल्याउनेछ, जसले इनपुट अप्टिकल सिग्नललाई एम्प्लीफाइ गर्नुपर्छ, त्यसैले अप्टिकल स्प्लिटरको अगाडि एक अप्टिकल एम्पलीफायर स्थापना गरिएको छ। अलग गरिएको अप्टिकल सिग्नलहरू त्यसपछि विभिन्न दरहरूको डिटेक्टरहरूद्वारा अप्टिकल / विद्युतीय रूपान्तरणको अधीनमा हुन्छन्, र अन्तमा दुई प्रकारका स्थिर विद्युतीय संकेत आउटपुटहरू प्राप्त हुन्छन्। यस समाधानको सबैभन्दा ठूलो बेफाइदा यो हो कि एक अप्टिकल एम्पलीफायर र 1: 2 अप्टिकल स्प्लिटर प्रयोग गरिन्छ, र अप्टिकल सिग्नललाई रूपान्तरण गर्न दुई डिटेक्टरहरू आवश्यक पर्दछ, जसले कार्यान्वयनको जटिलता बढाउँछ र लागत बढाउँछ।

FIG मा देखाइएको दोस्रो योजना मा। 3, इनपुट अप्टिकल सिग्नलले इलेक्ट्रिक डोमेनमा विभाजन प्राप्त गर्न डिटेक्टर र TIA मार्फत मात्र पास गर्न आवश्यक छ। यस समाधानको मूल कुरा TIA को छनोटमा छ, जसको लागि TIA सँग 1 ~ 10Gbit/s को ब्यान्डविथ हुनु आवश्यक छ, र एकै समयमा TIA सँग यस ब्यान्डविथ भित्र छिटो प्रतिक्रिया छ। TIA को हालको प्यारामिटर मार्फत मात्र प्रतिक्रिया मान छिटो प्राप्त गर्न सक्छ, प्राप्त संवेदनशीलता राम्रोसँग ग्यारेन्टी गर्न सकिन्छ। यो समाधानले कार्यान्वयनको जटिलतालाई धेरै कम गर्छ र लागतलाई नियन्त्रणमा राख्छ। वास्तविक डिजाइनमा, हामी सामान्यतया दोहोरो-दर बर्स्ट रिसेप्शन प्राप्त गर्न दोस्रो योजना छनौट गर्छौं।

2.3 प्राप्त अन्त्यमा हार्डवेयर सर्किटको डिजाइन

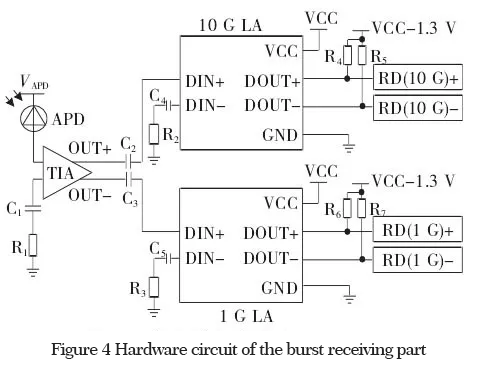

चित्र 4 बर्स्ट प्राप्त गर्ने भागको हार्डवेयर सर्किट हो। जब त्यहाँ एक बर्स्ट अप्टिकल इनपुट हुन्छ, APD ले अप्टिकल सिग्नललाई कमजोर विद्युतीय संकेतमा रूपान्तरण गर्छ र TIA मा पठाउँछ। संकेतलाई TIA द्वारा 10G वा 1G विद्युतीय संकेतमा विस्तार गरिएको छ। 10G विद्युतीय संकेत TIA को सकारात्मक युग्मन मार्फत 10G LA मा इनपुट हुन्छ, र 1G विद्युतीय संकेत TIA को नकारात्मक युग्मन मार्फत 1G LA मा इनपुट हुन्छ। क्यापेसिटर C2 र C3 10G र 1G AC-जोडिएको आउटपुट प्राप्त गर्न प्रयोग गरिने कपलिङ क्यापेसिटरहरू हुन्। AC-जोडिएको विधि छनौट गरिएको थियो किनभने यो DC-जोडिएको विधि भन्दा सरल छ।

जे होस्, AC युग्मनमा क्यापेसिटरको चार्ज र डिस्चार्ज हुन्छ, र सिग्नलको प्रतिक्रिया गति चार्ज र डिस्चार्ज समय स्थिरबाट प्रभावित हुन्छ, अर्थात्, सिग्नललाई समयमा प्रतिक्रिया दिन सकिँदैन। यो सुविधा रिसेप्शन सेटलिङ समय को एक निश्चित मात्रा गुमाउन बाध्य छ, त्यसैले यो AC युग्मन क्यापेसिटर कति ठूलो छनोट गर्न महत्त्वपूर्ण छ। यदि सानो युग्मन क्यापेसिटर चयन गरिएको छ भने, सेटलिङ समय छोटो गर्न सकिन्छ, र संकेत द्वारा प्रसारितONUप्रत्येक पटक स्लटमा रिसेप्शन प्रभावलाई असर नगरी पूर्ण रूपमा प्राप्त गर्न सकिन्छ किनभने रिसेप्शन सेटलिङ समय धेरै लामो छ र अर्को पटकको स्लटको आगमन।

यद्यपि, धेरै सानो क्षमताले युग्मन प्रभावलाई असर गर्छ र रिसेप्शनको स्थिरतालाई धेरै कम गर्छ। ठूलो क्यापेसिटन्सले प्रणालीको जिटर कम गर्न र प्राप्त गर्ने अन्तको संवेदनशीलता सुधार गर्न सक्छ। त्यसकारण, रिसेप्शन सेटलिङ समय र रिसेप्शन संवेदनशीलतालाई ध्यानमा राख्नको लागि, उपयुक्त युग्मन क्यापेसिटर C2 र C3 चयन गर्न आवश्यक छ। थप रूपमा, इनपुट विद्युतीय संकेतको स्थिरता सुनिश्चित गर्नको लागि, 50Ω को प्रतिरोधको साथ एक युग्मन क्यापेसिटर र मिल्दो प्रतिरोधक LA को नकारात्मक टर्मिनलमा जडान गरिएको छ।

LVPECL (लो भोल्टेज सकारात्मक उत्सर्जक युग्मन तर्क) प्रतिरोधक R4 र R5 (R6 र R7) र 10G (1G) LA द्वारा भिन्न संकेत आउटपुट मार्फत 2.0 V DC भोल्टेज स्रोतबाट बनेको सर्किट। बिजुली संकेत।

2.4 खण्ड सुरु गर्नुहोस्

10G EPON सिमेट्रिक को प्रसारण भागओएलटीअप्टिकल मोड्युल मुख्यतया 1.25 र 10G ट्रान्समिटिङको दुई भागमा विभाजन गरिएको छ, जसले क्रमशः 1490 र 1577 एनएमको तरंग लम्बाइको साथ डाउनलिङ्कमा संकेतहरू पठाउँछ। 10G ट्रान्समिटिङ पार्टलाई उदाहरणको रूपमा लिएर, 10G विभेदक संकेतहरूको जोडीले CDR (Clock Shaping) चिपमा प्रवेश गर्छ, 10G ड्राइभर चिपमा AC-जोडिएको हुन्छ, र अन्तमा 10G लेजरमा फरक रूपमा इनपुट गरिन्छ। किनभने तापक्रम परिवर्तनले लेजर उत्सर्जन तरंग दैर्ध्यमा ठूलो प्रभाव पार्छ, प्रोटोकल (प्रोटोकललाई 1575 ~ 1580nm आवश्यक छ) तरंगदैर्ध्यलाई स्थिर गर्नको लागि, TEC सर्किटको कार्य प्रवाह समायोजन गर्न आवश्यक छ, त्यसैले। कि आउटपुट तरंगदैर्ध्य राम्रोसँग नियन्त्रण गर्न सकिन्छ।

3. परीक्षण परिणाम र विश्लेषण

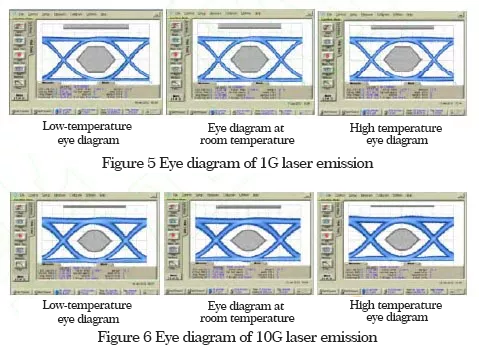

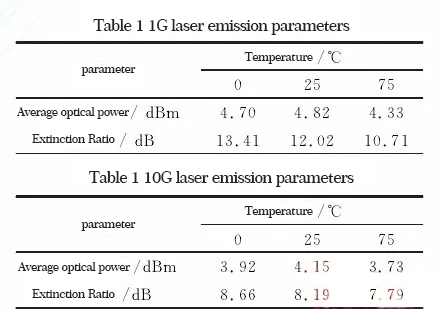

10G EPON सममितको मुख्य परीक्षण संकेतकहरूओएलटीअप्टिकल मोड्युलले रिसीभर सेटअप समय, रिसीभर संवेदनशीलता, र ट्रान्समिट आँखा रेखाचित्र समावेश गर्दछ। विशिष्ट परीक्षणहरू निम्नानुसार छन्:

(1) सेटअप समय प्राप्त गर्नुहोस्

-24.0 dBm को अपलिंक बर्स्ट अप्टिकल पावरको सामान्य कार्य वातावरण अन्तर्गत, बर्स्ट लाइट स्रोतबाट उत्सर्जित अप्टिकल सिग्नललाई मापन सुरूवात बिन्दुको रूपमा प्रयोग गरिन्छ, र मोड्युलले मापन अन्तिम बिन्दुको रूपमा पूर्ण विद्युतीय संकेत प्राप्त गर्दछ र स्थापना गर्दछ, बेवास्ता गर्दै। परीक्षण फाइबरमा प्रकाशको समय ढिलाइ। मापन गरिएको 1G बर्स्ट रिसेप्शन सेटअप समय 76.7 एनएस हो, जसले <400 एनएसको अन्तर्राष्ट्रिय मानक पूरा गर्दछ; 10G बर्स्ट रिसेप्शन सेटअप समय 241.8 ns हो, जसले <800 ns को अन्तर्राष्ट्रिय मानक पनि पूरा गर्दछ।

3. परीक्षण परिणाम र विश्लेषण

10G EPON सममितको मुख्य परीक्षण संकेतकहरूओएलटीअप्टिकल मोड्युलले रिसीभर सेटअप समय, रिसीभर संवेदनशीलता, र ट्रान्समिट आँखा रेखाचित्र समावेश गर्दछ। विशिष्ट परीक्षणहरू निम्नानुसार छन्:

(1) सेटअप समय प्राप्त गर्नुहोस्

-24.0 dBm को अपलिंक बर्स्ट अप्टिकल पावरको सामान्य कार्य वातावरण अन्तर्गत, बर्स्ट लाइट स्रोतबाट उत्सर्जित अप्टिकल सिग्नललाई मापन सुरूवात बिन्दुको रूपमा प्रयोग गरिन्छ, र मोड्युलले मापन अन्तिम बिन्दुको रूपमा पूर्ण विद्युतीय संकेत प्राप्त गर्दछ र स्थापना गर्दछ, बेवास्ता गर्दै। परीक्षण फाइबरमा प्रकाशको समय ढिलाइ। मापन गरिएको 1G बर्स्ट रिसेप्शन सेटअप समय 76.7 एनएस हो, जसले <400 एनएसको अन्तर्राष्ट्रिय मानक पूरा गर्दछ; 10G बर्स्ट रिसेप्शन सेटअप समय 241.8 ns हो, जसले <800 ns को अन्तर्राष्ट्रिय मानक पनि पूरा गर्दछ।