EPON ਸਿਸਟਮ ਵਿੱਚ, ਦਓ.ਐਲ.ਟੀਮਲਟੀਪਲ ਨਾਲ ਜੁੜਿਆ ਹੈONUs(ਆਪਟੀਕਲ ਨੈੱਟਵਰਕ ਯੂਨਿਟ) ਇੱਕ POS (ਪੈਸਿਵ ਆਪਟੀਕਲ ਸਪਲਿਟਰ) ਰਾਹੀਂ। EPON ਦੇ ਕੋਰ ਦੇ ਰੂਪ ਵਿੱਚ,ਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਸਿੱਧੇ 10G EPON ਸਿਸਟਮ ਦੇ ਸੰਚਾਲਨ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰਨਗੇ।

1. 10G EPON ਸਮਮਿਤੀ ਦੀ ਜਾਣ-ਪਛਾਣਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ

10G EPON ਸਮਮਿਤੀਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਅਪਲਿੰਕ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਅਤੇ ਡਾਊਨਲਿੰਕ ਨਿਰੰਤਰ ਪ੍ਰਸਾਰਣ ਮੋਡਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ, ਜੋ ਮੁੱਖ ਤੌਰ 'ਤੇ 10G EPON ਪ੍ਰਣਾਲੀਆਂ ਵਿੱਚ ਆਪਟੀਕਲ / ਇਲੈਕਟ੍ਰੀਕਲ ਪਰਿਵਰਤਨ ਲਈ ਵਰਤੇ ਜਾਂਦੇ ਹਨ।

ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਹਿੱਸੇ ਵਿੱਚ 1.25 ਅਤੇ 10.3125 Gbit/s ਦਰਾਂ 'ਤੇ ਇੱਕ TIA (ਟ੍ਰਾਂਸਿਮਪੀਡੈਂਸ ਐਂਪਲੀਫਾਇਰ), 1270 / 1310nm 'ਤੇ ਇੱਕ APD (ਅਵਲੈਂਚ ਫੋਟੋਡੀਓਡ), ਅਤੇ ਦੋ LA (ਸੀਮਤ ਐਂਪਲੀਫਾਇਰ) ਸ਼ਾਮਲ ਹੁੰਦੇ ਹਨ।

ਸੰਚਾਰਿਤ ਅੰਤ ਇੱਕ 10G EML (ਇਲੈਕਟਰੋ-ਅਬਜ਼ੋਰਪਸ਼ਨ ਮੋਡੂਲੇਸ਼ਨ ਲੇਜ਼ਰ) ਅਤੇ ਇੱਕ 1.25 Gbit / s DFB (ਡਿਸਟ੍ਰੀਬਿਊਟਡ ਫੀਡਬੈਕ ਲੇਜ਼ਰ) ਨਾਲ ਬਣਿਆ ਹੈ, ਅਤੇ ਇਸਦੀ ਐਮਿਸ਼ਨ ਵੇਵ-ਲੰਬਾਈ ਕ੍ਰਮਵਾਰ 1577 ਅਤੇ 1490nm ਹੈ।

ਡ੍ਰਾਈਵਿੰਗ ਸਰਕਟ ਵਿੱਚ ਇੱਕ ਸਥਿਰ 10G ਲੇਜ਼ਰ ਐਮੀਸ਼ਨ ਵੇਵ-ਲੰਬਾਈ ਨੂੰ ਬਣਾਈ ਰੱਖਣ ਲਈ ਇੱਕ ਡਿਜੀਟਲ APC (ਆਟੋਮੈਟਿਕ ਆਪਟੀਕਲ ਪਾਵਰ ਕੰਟਰੋਲ) ਸਰਕਟ ਅਤੇ ਇੱਕ TEC (ਤਾਪਮਾਨ ਮੁਆਵਜ਼ਾ) ਸਰਕਟ ਸ਼ਾਮਲ ਹੈ। SFF-8077iv4.5 ਪ੍ਰੋਟੋਕੋਲ ਦੇ ਅਨੁਸਾਰ ਪ੍ਰਸਾਰਣ ਅਤੇ ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਪੈਰਾਮੀਟਰ ਨਿਗਰਾਨੀ ਨੂੰ ਸਿੰਗਲ ਚਿੱਪ ਮਾਈਕ੍ਰੋਕੰਪਿਊਟਰ ਦੁਆਰਾ ਲਾਗੂ ਕੀਤਾ ਜਾਂਦਾ ਹੈ।

ਕਿਉਕਿ ਦੇ ਪ੍ਰਾਪਤ ਅੰਤਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ, ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ ਖਾਸ ਤੌਰ 'ਤੇ ਮਹੱਤਵਪੂਰਨ ਹੁੰਦਾ ਹੈ। ਜੇਕਰ ਰਿਸੈਪਸ਼ਨ ਦਾ ਨਿਪਟਾਰਾ ਕਰਨ ਦਾ ਸਮਾਂ ਲੰਬਾ ਹੈ, ਤਾਂ ਇਹ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਨੂੰ ਬਹੁਤ ਪ੍ਰਭਾਵਿਤ ਕਰੇਗਾ, ਅਤੇ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਨੂੰ ਸਹੀ ਢੰਗ ਨਾਲ ਕੰਮ ਨਾ ਕਰਨ ਦਾ ਕਾਰਨ ਵੀ ਬਣ ਸਕਦਾ ਹੈ। IEEE 802.3av ਪ੍ਰੋਟੋਕੋਲ ਦੀਆਂ ਲੋੜਾਂ ਦੇ ਅਨੁਸਾਰ, ਇੱਕ 1.25Gbit / s ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਦੀ ਸਥਾਪਨਾ ਦਾ ਸਮਾਂ <400 ns ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ, ਅਤੇ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੰਵੇਦਨਸ਼ੀਲਤਾ 10-12 ਦੀ ਇੱਕ ਬਿੱਟ ਗਲਤੀ ਦਰ ਦੇ ਨਾਲ <-29.78 dBm ਹੋਣੀ ਚਾਹੀਦੀ ਹੈ; ਅਤੇ 10.3125 Gbit/s ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ <800ns ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ, ਅਤੇ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੰਵੇਦਨਸ਼ੀਲਤਾ 10-3 ਦੀ ਇੱਕ ਬਿੱਟ ਗਲਤੀ ਦਰ ਦੇ ਨਾਲ <-28.0 dBm ਹੋਣੀ ਚਾਹੀਦੀ ਹੈ।

2.10G EPON ਸਮਮਿਤੀਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਡਿਜ਼ਾਈਨ

2.1 ਡਿਜ਼ਾਈਨ ਸਕੀਮ

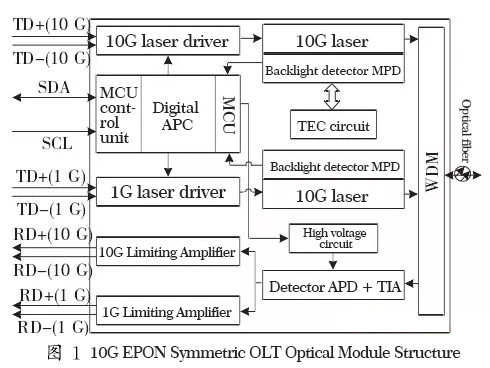

10G EPON ਸਮਮਿਤੀਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਇੱਕ ਟ੍ਰਿਪਲੈਕਸਰ (ਸਿੰਗਲ-ਫਾਈਬਰ ਥ੍ਰੀ-ਵੇ ਮੋਡੀਊਲ), ਸੰਚਾਰਿਤ, ਪ੍ਰਾਪਤ ਕਰਨਾ ਅਤੇ ਨਿਗਰਾਨੀ ਨਾਲ ਬਣਿਆ ਹੁੰਦਾ ਹੈ। ਟ੍ਰਿਪਲੈਕਸਰ ਵਿੱਚ ਦੋ ਲੇਜ਼ਰ ਅਤੇ ਇੱਕ ਡਿਟੈਕਟਰ ਸ਼ਾਮਲ ਹਨ। ਪ੍ਰਸਾਰਿਤ ਰੋਸ਼ਨੀ ਅਤੇ ਪ੍ਰਾਪਤ ਹੋਈ ਰੋਸ਼ਨੀ ਨੂੰ ਸਿੰਗਲ-ਫਾਈਬਰ ਬਾਈਡਾਇਰੈਕਸ਼ਨਲ ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਡਬਲਯੂਡੀਐਮ (ਵੇਵਲੈਂਥ ਡਿਵੀਜ਼ਨ ਮਲਟੀਪਲੈਕਸਰ) ਦੁਆਰਾ ਆਪਟੀਕਲ ਡਿਵਾਈਸ ਵਿੱਚ ਏਕੀਕ੍ਰਿਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਇਸਦੀ ਬਣਤਰ ਚਿੱਤਰ 1 ਵਿੱਚ ਦਿਖਾਈ ਗਈ ਹੈ।

ਪ੍ਰਸਾਰਣ ਕਰਨ ਵਾਲੇ ਹਿੱਸੇ ਵਿੱਚ ਦੋ ਲੇਜ਼ਰ ਹੁੰਦੇ ਹਨ, ਜਿਸਦਾ ਮੁੱਖ ਕੰਮ ਕ੍ਰਮਵਾਰ 1G ਅਤੇ 10G ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲਾਂ ਨੂੰ ਆਪਟੀਕਲ ਸਿਗਨਲਾਂ ਵਿੱਚ ਬਦਲਣਾ ਅਤੇ ਇੱਕ ਡਿਜੀਟਲ APC ਸਰਕਟ ਦੁਆਰਾ ਇੱਕ ਬੰਦ ਲੂਪ ਅਵਸਥਾ ਵਿੱਚ ਆਪਟੀਕਲ ਪਾਵਰ ਸਥਿਰਤਾ ਨੂੰ ਕਾਇਮ ਰੱਖਣਾ ਹੈ। ਉਸੇ ਸਮੇਂ, ਸਿੰਗਲ-ਚਿੱਪ ਮਾਈਕ੍ਰੋਕੰਪਿਊਟਰ ਸਿਸਟਮ ਦੁਆਰਾ ਲੋੜੀਂਦੇ ਅਲੋਪ ਅਨੁਪਾਤ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਮੋਡੂਲੇਸ਼ਨ ਕਰੰਟ ਦੀ ਤੀਬਰਤਾ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਦਾ ਹੈ। TEC ਸਰਕਟ ਨੂੰ 10G ਟ੍ਰਾਂਸਮੀਟਿੰਗ ਸਰਕਟ ਵਿੱਚ ਜੋੜਿਆ ਗਿਆ ਹੈ, ਜੋ 10G ਲੇਜ਼ਰ ਦੀ ਆਉਟਪੁੱਟ ਤਰੰਗ ਲੰਬਾਈ ਨੂੰ ਬਹੁਤ ਸਥਿਰ ਕਰਦਾ ਹੈ। ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲਾ ਹਿੱਸਾ ਖੋਜੇ ਗਏ ਬਰਸਟ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਵਿੱਚ ਬਦਲਣ ਲਈ APD ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ, ਅਤੇ ਇਸਨੂੰ ਐਮਪਲੀਫਿਕੇਸ਼ਨ ਅਤੇ ਆਕਾਰ ਦੇਣ ਤੋਂ ਬਾਅਦ ਆਉਟਪੁੱਟ ਕਰਦਾ ਹੈ। ਇਹ ਯਕੀਨੀ ਬਣਾਉਣ ਲਈ ਕਿ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਆਦਰਸ਼ ਸੀਮਾ ਤੱਕ ਪਹੁੰਚ ਸਕਦੀ ਹੈ, ਵੱਖ-ਵੱਖ ਤਾਪਮਾਨਾਂ 'ਤੇ APD ਨੂੰ ਸਥਿਰ ਉੱਚ ਦਬਾਅ ਪ੍ਰਦਾਨ ਕਰਨਾ ਜ਼ਰੂਰੀ ਹੈ। ਇੱਕ-ਚਿੱਪ ਕੰਪਿਊਟਰ APD ਉੱਚ-ਵੋਲਟੇਜ ਸਰਕਟ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਕੇ ਇਸ ਟੀਚੇ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ।

2.2 ਦੋਹਰੀ ਦਰ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਨੂੰ ਲਾਗੂ ਕਰਨਾ

10G EPON ਸਿਮਟ੍ਰਿਕ ਦਾ ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲਾ ਹਿੱਸਾਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਬਰਸਟ ਰਿਸੀਵਿੰਗ ਵਿਧੀ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ। ਇਸਨੂੰ 1.25 ਅਤੇ 10.3125 Gbit/s ਦੀਆਂ ਦੋ ਵੱਖ-ਵੱਖ ਦਰਾਂ ਦੇ ਬਰਸਟ ਸਿਗਨਲ ਪ੍ਰਾਪਤ ਕਰਨ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਜਿਸ ਲਈ ਸਥਿਰ ਆਉਟਪੁੱਟ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਹਿੱਸੇ ਨੂੰ ਇਹਨਾਂ ਦੋ ਵੱਖ-ਵੱਖ ਦਰਾਂ ਦੇ ਆਪਟੀਕਲ ਸਿਗਨਲਾਂ ਨੂੰ ਚੰਗੀ ਤਰ੍ਹਾਂ ਵੱਖ ਕਰਨ ਦੇ ਯੋਗ ਹੋਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਦੀ ਦੋਹਰੀ ਦਰ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਨੂੰ ਲਾਗੂ ਕਰਨ ਲਈ ਦੋ ਸਕੀਮਾਂਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਇੱਥੇ ਪ੍ਰਸਤਾਵਿਤ ਹਨ।

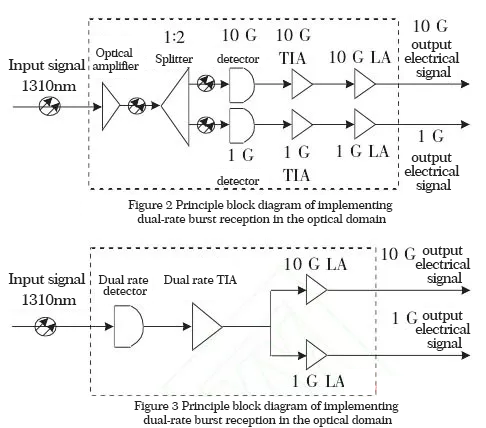

ਕਿਉਂਕਿ ਇਨਪੁਟ ਆਪਟੀਕਲ ਸਿਗਨਲ TDMA (ਟਾਈਮ ਡਿਵੀਜ਼ਨ ਮਲਟੀਪਲ ਐਕਸੈਸ) ਤਕਨਾਲੋਜੀ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ, ਉਸੇ ਸਮੇਂ ਬਰਸਟ ਲਾਈਟ ਦੀ ਸਿਰਫ ਇੱਕ ਦਰ ਮੌਜੂਦ ਹੋ ਸਕਦੀ ਹੈ। ਇੰਪੁੱਟ ਸਿਗਨਲ ਨੂੰ ਆਪਟੀਕਲ ਡੋਮੇਨ ਵਿੱਚ ਇੱਕ 1: 2 ਆਪਟੀਕਲ ਸਪਲਿਟਰ ਰਾਹੀਂ ਵੱਖ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 2 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ। ਜਾਂ 1G ਅਤੇ 10G ਆਪਟੀਕਲ ਸਿਗਨਲਾਂ ਨੂੰ ਕਮਜ਼ੋਰ ਬਿਜਲਈ ਸਿਗਨਲਾਂ ਵਿੱਚ ਬਦਲਣ ਲਈ ਸਿਰਫ ਇੱਕ ਉੱਚ-ਸਪੀਡ ਡਿਟੈਕਟਰ ਦੀ ਵਰਤੋਂ ਕਰੋ, ਅਤੇ ਫਿਰ ਦੋ ਇਲੈਕਟ੍ਰੀਕਲ ਨੂੰ ਵੱਖ ਕਰੋ। ਇੱਕ ਵੱਡੀ ਬੈਂਡਵਿਡਥ TIA ਰਾਹੀਂ ਵੱਖ-ਵੱਖ ਦਰਾਂ ਵਾਲੇ ਸਿਗਨਲ, ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 3 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ।

ਚਿੱਤਰ 2 ਵਿੱਚ ਦਿਖਾਈ ਗਈ ਪਹਿਲੀ ਸਕੀਮ ਇੱਕ ਨਿਸ਼ਚਿਤ ਸੰਮਿਲਨ ਨੁਕਸਾਨ ਲਿਆਏਗੀ ਜਦੋਂ ਰੋਸ਼ਨੀ 1: 2 ਆਪਟੀਕਲ ਸਪਲਿਟਰ ਵਿੱਚੋਂ ਲੰਘਦੀ ਹੈ, ਜੋ ਕਿ ਇਨਪੁਟ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਵਧਾਉਂਦੀ ਹੈ, ਇਸਲਈ ਆਪਟੀਕਲ ਸਪਲਿਟਰ ਦੇ ਸਾਹਮਣੇ ਇੱਕ ਆਪਟੀਕਲ ਐਂਪਲੀਫਾਇਰ ਸਥਾਪਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਵੱਖ ਕੀਤੇ ਆਪਟੀਕਲ ਸਿਗਨਲਾਂ ਨੂੰ ਫਿਰ ਵੱਖ-ਵੱਖ ਦਰਾਂ ਦੇ ਡਿਟੈਕਟਰਾਂ ਦੁਆਰਾ ਆਪਟੀਕਲ / ਇਲੈਕਟ੍ਰੀਕਲ ਪਰਿਵਰਤਨ ਦੇ ਅਧੀਨ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਅੰਤ ਵਿੱਚ ਦੋ ਕਿਸਮ ਦੇ ਸਥਿਰ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਆਉਟਪੁੱਟ ਪ੍ਰਾਪਤ ਕੀਤੇ ਜਾਂਦੇ ਹਨ। ਇਸ ਹੱਲ ਦਾ ਸਭ ਤੋਂ ਵੱਡਾ ਨੁਕਸਾਨ ਇਹ ਹੈ ਕਿ ਇੱਕ ਆਪਟੀਕਲ ਐਂਪਲੀਫਾਇਰ ਅਤੇ ਇੱਕ 1: 2 ਆਪਟੀਕਲ ਸਪਲਿਟਰ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਬਦਲਣ ਲਈ ਦੋ ਡਿਟੈਕਟਰਾਂ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਜੋ ਲਾਗੂ ਕਰਨ ਦੀ ਗੁੰਝਲਤਾ ਨੂੰ ਵਧਾਉਂਦਾ ਹੈ ਅਤੇ ਲਾਗਤ ਵਧਾਉਂਦਾ ਹੈ।

FIG ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਦੂਜੀ ਸਕੀਮ ਵਿੱਚ. 3, ਇੰਪੁੱਟ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਇਲੈਕਟ੍ਰਿਕ ਡੋਮੇਨ ਵਿੱਚ ਵੱਖ ਹੋਣ ਲਈ ਸਿਰਫ ਇੱਕ ਡਿਟੈਕਟਰ ਅਤੇ ਇੱਕ TIA ਵਿੱਚੋਂ ਲੰਘਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਇਸ ਹੱਲ ਦਾ ਮੂਲ ਟੀਆਈਏ ਦੀ ਚੋਣ ਵਿੱਚ ਹੈ, ਜਿਸ ਲਈ TIA ਨੂੰ 1 ~ 10Gbit/s ਦੀ ਬੈਂਡਵਿਡਥ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਉਸੇ ਸਮੇਂ TIA ਕੋਲ ਇਸ ਬੈਂਡਵਿਡਥ ਦੇ ਅੰਦਰ ਤੇਜ਼ ਜਵਾਬ ਹੁੰਦਾ ਹੈ। ਸਿਰਫ TIA ਦੇ ਮੌਜੂਦਾ ਪੈਰਾਮੀਟਰ ਦੁਆਰਾ ਜਵਾਬ ਮੁੱਲ ਨੂੰ ਤੇਜ਼ੀ ਨਾਲ ਪ੍ਰਾਪਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੀ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਦੀ ਚੰਗੀ ਤਰ੍ਹਾਂ ਗਾਰੰਟੀ ਦਿੱਤੀ ਜਾ ਸਕਦੀ ਹੈ. ਇਹ ਹੱਲ ਲਾਗੂ ਕਰਨ ਦੀ ਗੁੰਝਲਤਾ ਨੂੰ ਬਹੁਤ ਘਟਾਉਂਦਾ ਹੈ ਅਤੇ ਲਾਗਤਾਂ ਨੂੰ ਨਿਯੰਤਰਣ ਵਿੱਚ ਰੱਖਦਾ ਹੈ। ਅਸਲ ਡਿਜ਼ਾਇਨ ਵਿੱਚ, ਅਸੀਂ ਆਮ ਤੌਰ 'ਤੇ ਦੋਹਰੇ-ਦਰ ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਦੂਜੀ ਸਕੀਮ ਚੁਣਦੇ ਹਾਂ।

2.3 ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਸਿਰੇ 'ਤੇ ਹਾਰਡਵੇਅਰ ਸਰਕਟ ਦਾ ਡਿਜ਼ਾਈਨ

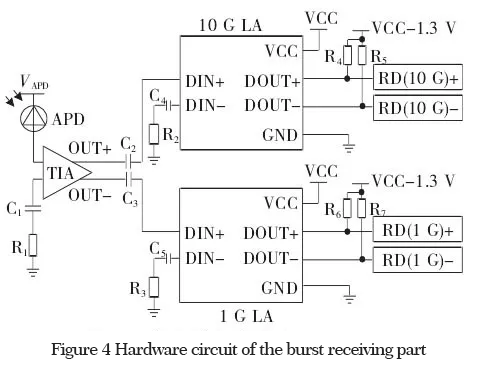

ਚਿੱਤਰ 4 ਬਰਸਟ ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਹਿੱਸੇ ਦਾ ਹਾਰਡਵੇਅਰ ਸਰਕਟ ਹੈ। ਜਦੋਂ ਇੱਕ ਬਰਸਟ ਆਪਟੀਕਲ ਇਨਪੁਟ ਹੁੰਦਾ ਹੈ, ਤਾਂ APD ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਇੱਕ ਕਮਜ਼ੋਰ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਵਿੱਚ ਬਦਲਦਾ ਹੈ ਅਤੇ ਇਸਨੂੰ TIA ਨੂੰ ਭੇਜਦਾ ਹੈ। ਸਿਗਨਲ ਨੂੰ TIA ਦੁਆਰਾ ਇੱਕ 10G ਜਾਂ 1G ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਵਿੱਚ ਵਧਾਇਆ ਜਾਂਦਾ ਹੈ। 10G ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ TIA ਦੇ ਸਕਾਰਾਤਮਕ ਜੋੜ ਰਾਹੀਂ 10G LA ਵਿੱਚ ਇਨਪੁਟ ਹੁੰਦਾ ਹੈ, ਅਤੇ 1G ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ TIA ਦੇ ਨਕਾਰਾਤਮਕ ਜੋੜ ਰਾਹੀਂ 1G LA ਵਿੱਚ ਇਨਪੁਟ ਹੁੰਦਾ ਹੈ। Capacitors C2 ਅਤੇ C3 10G ਅਤੇ 1G AC-ਕਪਲਡ ਆਉਟਪੁੱਟ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਵਰਤੇ ਜਾਂਦੇ ਕਪਲਿੰਗ ਕੈਪਸੀਟਰ ਹਨ। AC-ਜੁੜੇ ਢੰਗ ਨੂੰ ਚੁਣਿਆ ਗਿਆ ਸੀ ਕਿਉਂਕਿ ਇਹ DC-ਜੋੜੇ ਵਾਲੇ ਢੰਗ ਨਾਲੋਂ ਸਰਲ ਹੈ।

ਹਾਲਾਂਕਿ, AC ਕਪਲਿੰਗ ਵਿੱਚ ਕੈਪੀਸੀਟਰ ਦਾ ਚਾਰਜ ਅਤੇ ਡਿਸਚਾਰਜ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਸਿਗਨਲ ਦੀ ਪ੍ਰਤੀਕਿਰਿਆ ਦੀ ਗਤੀ ਚਾਰਜ ਅਤੇ ਡਿਸਚਾਰਜ ਟਾਈਮ ਸਥਿਰਾਂ ਦੁਆਰਾ ਪ੍ਰਭਾਵਿਤ ਹੁੰਦੀ ਹੈ, ਯਾਨੀ, ਸਿਗਨਲ ਨੂੰ ਸਮੇਂ ਸਿਰ ਜਵਾਬ ਨਹੀਂ ਦਿੱਤਾ ਜਾ ਸਕਦਾ ਹੈ। ਇਹ ਵਿਸ਼ੇਸ਼ਤਾ ਰਿਸੈਪਸ਼ਨ ਦੇ ਨਿਪਟਾਰੇ ਦੇ ਸਮੇਂ ਦੀ ਇੱਕ ਨਿਸ਼ਚਿਤ ਮਾਤਰਾ ਨੂੰ ਗੁਆਉਣ ਲਈ ਪਾਬੰਦ ਹੈ, ਇਸਲਈ ਇਹ ਚੁਣਨਾ ਮਹੱਤਵਪੂਰਨ ਹੈ ਕਿ AC ਕਪਲਿੰਗ ਕੈਪੇਸੀਟਰ ਕਿੰਨਾ ਵੱਡਾ ਹੈ। ਜੇਕਰ ਇੱਕ ਛੋਟਾ ਕਪਲਿੰਗ ਕੈਪੇਸੀਟਰ ਚੁਣਿਆ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਸੈਟਲ ਹੋਣ ਦਾ ਸਮਾਂ ਛੋਟਾ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਅਤੇ ਸਿਗਨਲ ਦੁਆਰਾ ਪ੍ਰਸਾਰਿਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।ਓ.ਐਨ.ਯੂਹਰ ਵਾਰ ਸਲਾਟ ਵਿੱਚ ਰਿਸੈਪਸ਼ਨ ਪ੍ਰਭਾਵ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕੀਤੇ ਬਿਨਾਂ ਪੂਰੀ ਤਰ੍ਹਾਂ ਪ੍ਰਾਪਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ ਕਿਉਂਕਿ ਰਿਸੈਪਸ਼ਨ ਦਾ ਨਿਪਟਾਰਾ ਕਰਨ ਦਾ ਸਮਾਂ ਬਹੁਤ ਲੰਬਾ ਹੈ ਅਤੇ ਅਗਲੀ ਵਾਰ ਸਲਾਟ ਦੀ ਆਮਦ।

ਹਾਲਾਂਕਿ, ਬਹੁਤ ਘੱਟ ਸਮਰੱਥਾ ਕਪਲਿੰਗ ਪ੍ਰਭਾਵ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰੇਗੀ ਅਤੇ ਰਿਸੈਪਸ਼ਨ ਦੀ ਸਥਿਰਤਾ ਨੂੰ ਬਹੁਤ ਘੱਟ ਕਰੇਗੀ। ਵੱਡੀ ਸਮਰੱਥਾ ਸਿਸਟਮ ਦੇ ਘਬਰਾਹਟ ਨੂੰ ਘਟਾ ਸਕਦੀ ਹੈ ਅਤੇ ਪ੍ਰਾਪਤ ਕਰਨ ਵਾਲੇ ਸਿਰੇ ਦੀ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਨੂੰ ਸੁਧਾਰ ਸਕਦੀ ਹੈ। ਇਸ ਲਈ, ਰਿਸੈਪਸ਼ਨ ਦੇ ਨਿਪਟਾਰੇ ਦੇ ਸਮੇਂ ਅਤੇ ਰਿਸੈਪਸ਼ਨ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਨੂੰ ਧਿਆਨ ਵਿੱਚ ਰੱਖਣ ਲਈ, ਢੁਕਵੇਂ ਕਪਲਿੰਗ ਕੈਪਸੀਟਰ C2 ਅਤੇ C3 ਦੀ ਚੋਣ ਕਰਨ ਦੀ ਲੋੜ ਹੈ। ਇਸ ਤੋਂ ਇਲਾਵਾ, ਇੰਪੁੱਟ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਦੀ ਸਥਿਰਤਾ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਣ ਲਈ, 50Ω ਦੇ ਪ੍ਰਤੀਰੋਧ ਦੇ ਨਾਲ ਇੱਕ ਕਪਲਿੰਗ ਕੈਪਸੀਟਰ ਅਤੇ ਇੱਕ ਮੇਲ ਖਾਂਦਾ ਰੋਧਕ LA ਦੇ ਨਕਾਰਾਤਮਕ ਟਰਮੀਨਲ ਨਾਲ ਜੁੜੇ ਹੋਏ ਹਨ।

LVPECL (ਘੱਟ ਵੋਲਟੇਜ ਸਕਾਰਾਤਮਕ ਐਮੀਟਰ ਕਪਲਿੰਗ ਲੌਜਿਕ) 10G (1G) LA ਦੁਆਰਾ ਡਿਫਰੈਂਸ਼ੀਅਲ ਸਿਗਨਲ ਆਉਟਪੁੱਟ ਦੁਆਰਾ ਰੋਧਕ R4 ਅਤੇ R5 (R6 ਅਤੇ R7) ਅਤੇ ਇੱਕ 2.0 V DC ਵੋਲਟੇਜ ਸਰੋਤ ਨਾਲ ਬਣਿਆ ਸਰਕਟ। ਇਲੈਕਟ੍ਰਿਕ ਸਿਗਨਲ.

2.4 ਸੈਕਸ਼ਨ ਲਾਂਚ ਕਰੋ

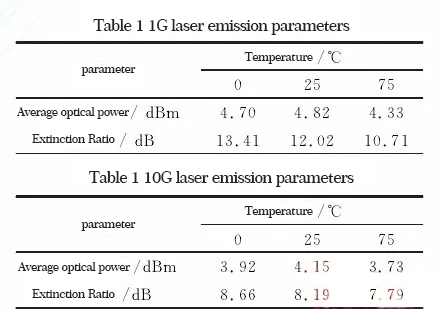

10G EPON ਸਮਮਿਤੀ ਦਾ ਪ੍ਰਸਾਰਣ ਕਰਨ ਵਾਲਾ ਹਿੱਸਾਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਮੁੱਖ ਤੌਰ 'ਤੇ 1.25 ਅਤੇ 10G ਟ੍ਰਾਂਸਮੀਟਿੰਗ ਦੇ ਦੋ ਹਿੱਸਿਆਂ ਵਿੱਚ ਵੰਡਿਆ ਗਿਆ ਹੈ, ਜੋ ਕ੍ਰਮਵਾਰ ਡਾਊਨਲਿੰਕ ਨੂੰ 1490 ਅਤੇ 1577 nm ਦੀ ਤਰੰਗ ਲੰਬਾਈ ਵਾਲੇ ਸਿਗਨਲ ਭੇਜਦੇ ਹਨ। 10G ਪ੍ਰਸਾਰਣ ਕਰਨ ਵਾਲੇ ਹਿੱਸੇ ਨੂੰ ਇੱਕ ਉਦਾਹਰਨ ਵਜੋਂ ਲੈਂਦੇ ਹੋਏ, 10G ਡਿਫਰੈਂਸ਼ੀਅਲ ਸਿਗਨਲ ਦੀ ਇੱਕ ਜੋੜਾ ਇੱਕ CDR (ਕਲੌਕ ਸ਼ੇਪਿੰਗ) ਚਿੱਪ ਵਿੱਚ ਦਾਖਲ ਹੁੰਦਾ ਹੈ, ਇੱਕ 10G ਡਰਾਈਵਰ ਚਿੱਪ ਨਾਲ AC-ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਅੰਤ ਵਿੱਚ ਇੱਕ 10G ਲੇਜ਼ਰ ਵਿੱਚ ਵੱਖਰੇ ਤੌਰ 'ਤੇ ਇਨਪੁਟ ਹੁੰਦਾ ਹੈ। ਕਿਉਂਕਿ ਤਾਪਮਾਨ ਵਿੱਚ ਤਬਦੀਲੀ ਦਾ ਲੇਜ਼ਰ ਐਮੀਸ਼ਨ ਵੇਵ-ਲੰਬਾਈ ਉੱਤੇ ਬਹੁਤ ਪ੍ਰਭਾਵ ਪਵੇਗਾ, ਪ੍ਰੋਟੋਕੋਲ (ਪ੍ਰੋਟੋਕੋਲ ਲਈ 1575 ~ 1580nm) ਦੁਆਰਾ ਲੋੜੀਂਦੇ ਪੱਧਰ ਤੱਕ ਤਰੰਗ-ਲੰਬਾਈ ਨੂੰ ਸਥਿਰ ਕਰਨ ਲਈ, TEC ਸਰਕਟ ਦੇ ਕਾਰਜਸ਼ੀਲ ਕਰੰਟ ਨੂੰ ਐਡਜਸਟ ਕਰਨ ਦੀ ਲੋੜ ਹੈ, ਇਸ ਲਈ ਕਿ ਆਉਟਪੁੱਟ ਵੇਵ-ਲੰਬਾਈ ਨੂੰ ਚੰਗੀ ਤਰ੍ਹਾਂ ਕੰਟਰੋਲ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।

3. ਟੈਸਟ ਦੇ ਨਤੀਜੇ ਅਤੇ ਵਿਸ਼ਲੇਸ਼ਣ

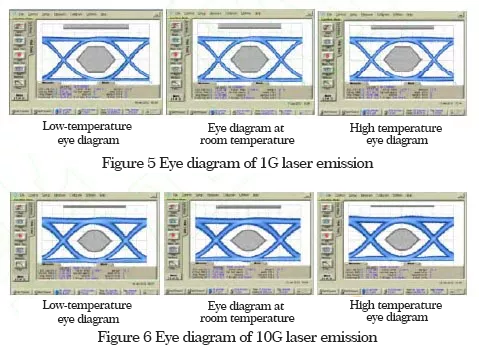

10G EPON ਸਮਮਿਤੀ ਦੇ ਮੁੱਖ ਟੈਸਟ ਸੂਚਕਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਵਿੱਚ ਰਿਸੀਵਰ ਸੈੱਟਅੱਪ ਸਮਾਂ, ਰਿਸੀਵਰ ਸੰਵੇਦਨਸ਼ੀਲਤਾ, ਅਤੇ ਪ੍ਰਸਾਰਿਤ ਅੱਖਾਂ ਦਾ ਚਿੱਤਰ ਸ਼ਾਮਲ ਹੁੰਦਾ ਹੈ। ਖਾਸ ਟੈਸਟ ਹੇਠ ਲਿਖੇ ਅਨੁਸਾਰ ਹਨ:

(1) ਸੈੱਟਅੱਪ ਸਮਾਂ ਪ੍ਰਾਪਤ ਕਰੋ

-24.0 dBm ਦੀ ਅਪਲਿੰਕ ਬਰਸਟ ਆਪਟੀਕਲ ਪਾਵਰ ਦੇ ਆਮ ਕਾਰਜਸ਼ੀਲ ਵਾਤਾਵਰਣ ਦੇ ਤਹਿਤ, ਬਰਸਟ ਲਾਈਟ ਸਰੋਤ ਦੁਆਰਾ ਨਿਕਲਣ ਵਾਲੇ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਮਾਪ ਦੇ ਸ਼ੁਰੂਆਤੀ ਬਿੰਦੂ ਵਜੋਂ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਮੋਡੀਊਲ ਮਾਪ ਦੇ ਅੰਤ ਬਿੰਦੂ ਦੇ ਤੌਰ ਤੇ ਇੱਕ ਪੂਰਨ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ ਅਤੇ ਸਥਾਪਿਤ ਕਰਦਾ ਹੈ, ਨੂੰ ਨਜ਼ਰਅੰਦਾਜ਼ ਕਰਦੇ ਹੋਏ। ਟੈਸਟ ਫਾਈਬਰ ਵਿੱਚ ਰੋਸ਼ਨੀ ਦੇ ਸਮੇਂ ਵਿੱਚ ਦੇਰੀ। ਮਾਪਿਆ ਗਿਆ 1G ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ 76.7 ns ਹੈ, ਜੋ <400 ns ਦੇ ਅੰਤਰਰਾਸ਼ਟਰੀ ਮਿਆਰ ਨੂੰ ਪੂਰਾ ਕਰਦਾ ਹੈ; 10G ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ 241.8 ns ਹੈ, ਜੋ <800 ns ਦੇ ਅੰਤਰਰਾਸ਼ਟਰੀ ਮਿਆਰ ਨੂੰ ਵੀ ਪੂਰਾ ਕਰਦਾ ਹੈ।

3. ਟੈਸਟ ਦੇ ਨਤੀਜੇ ਅਤੇ ਵਿਸ਼ਲੇਸ਼ਣ

10G EPON ਸਮਮਿਤੀ ਦੇ ਮੁੱਖ ਟੈਸਟ ਸੂਚਕਓ.ਐਲ.ਟੀਆਪਟੀਕਲ ਮੋਡੀਊਲ ਵਿੱਚ ਰਿਸੀਵਰ ਸੈੱਟਅੱਪ ਸਮਾਂ, ਰਿਸੀਵਰ ਸੰਵੇਦਨਸ਼ੀਲਤਾ, ਅਤੇ ਪ੍ਰਸਾਰਿਤ ਅੱਖਾਂ ਦਾ ਚਿੱਤਰ ਸ਼ਾਮਲ ਹੁੰਦਾ ਹੈ। ਖਾਸ ਟੈਸਟ ਹੇਠ ਲਿਖੇ ਅਨੁਸਾਰ ਹਨ:

(1) ਸੈੱਟਅੱਪ ਸਮਾਂ ਪ੍ਰਾਪਤ ਕਰੋ

-24.0 dBm ਦੀ ਅਪਲਿੰਕ ਬਰਸਟ ਆਪਟੀਕਲ ਪਾਵਰ ਦੇ ਆਮ ਕਾਰਜਸ਼ੀਲ ਵਾਤਾਵਰਣ ਦੇ ਤਹਿਤ, ਬਰਸਟ ਲਾਈਟ ਸਰੋਤ ਦੁਆਰਾ ਨਿਕਲਣ ਵਾਲੇ ਆਪਟੀਕਲ ਸਿਗਨਲ ਨੂੰ ਮਾਪ ਦੇ ਸ਼ੁਰੂਆਤੀ ਬਿੰਦੂ ਵਜੋਂ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਮੋਡੀਊਲ ਮਾਪ ਦੇ ਅੰਤ ਬਿੰਦੂ ਦੇ ਤੌਰ ਤੇ ਇੱਕ ਪੂਰਨ ਇਲੈਕਟ੍ਰੀਕਲ ਸਿਗਨਲ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ ਅਤੇ ਸਥਾਪਿਤ ਕਰਦਾ ਹੈ, ਨੂੰ ਨਜ਼ਰਅੰਦਾਜ਼ ਕਰਦੇ ਹੋਏ। ਟੈਸਟ ਫਾਈਬਰ ਵਿੱਚ ਰੋਸ਼ਨੀ ਦੇ ਸਮੇਂ ਵਿੱਚ ਦੇਰੀ। ਮਾਪਿਆ ਗਿਆ 1G ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ 76.7 ns ਹੈ, ਜੋ <400 ns ਦੇ ਅੰਤਰਰਾਸ਼ਟਰੀ ਮਿਆਰ ਨੂੰ ਪੂਰਾ ਕਰਦਾ ਹੈ; 10G ਬਰਸਟ ਰਿਸੈਪਸ਼ਨ ਸੈੱਟਅੱਪ ਸਮਾਂ 241.8 ns ਹੈ, ਜੋ <800 ns ਦੇ ਅੰਤਰਰਾਸ਼ਟਰੀ ਮਿਆਰ ਨੂੰ ਵੀ ਪੂਰਾ ਕਰਦਾ ਹੈ।