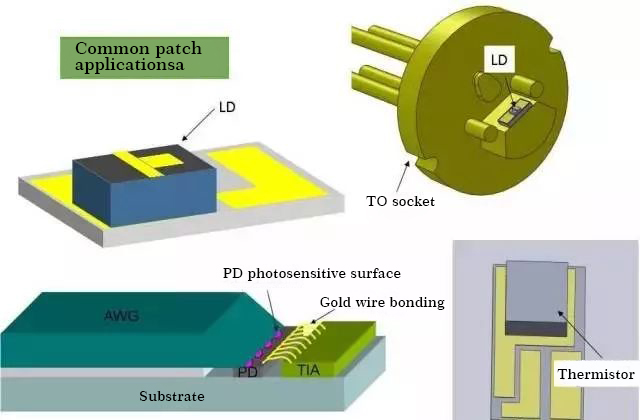

Det första steget i processen att ta emot ett chip kan vara patchen; en TO inkluderar en patch som värmesänker till TO-uttaget, ett chip som LDs till kylflänsen och en bakgrundsbelysning PD;

Den specifika monteringsprocessen kan vara mycket annorlunda: objektet som ska fästas är vanligtvis ett LD / PD-chip, eller TIA, motstånd / kondensator; placeringen kan utföras på en kylfläns av aluminiumnitrid eller direkt på kretskortet; placeringen Eutektisk svetsning eller ledande lim kan användas; lappen kan bara kräva tiotals eller till och med hundratals mikrometers noggrannhet, såsom TIA, motstånd och submikrons noggrannhet, såsom passiv flip-chipsvetsning.

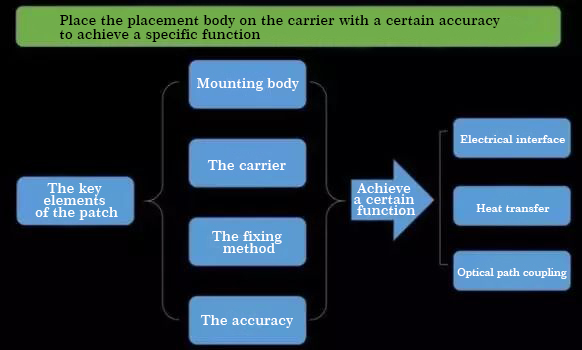

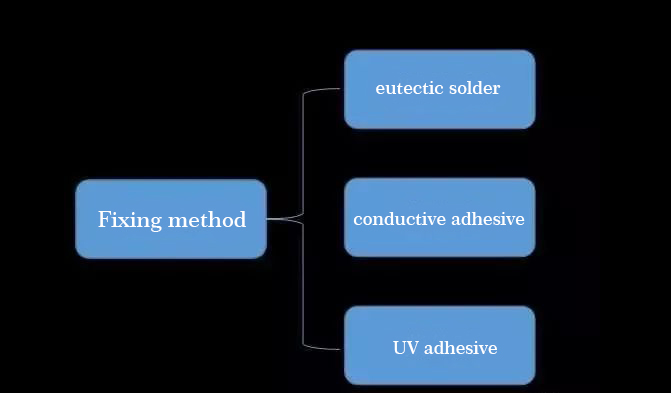

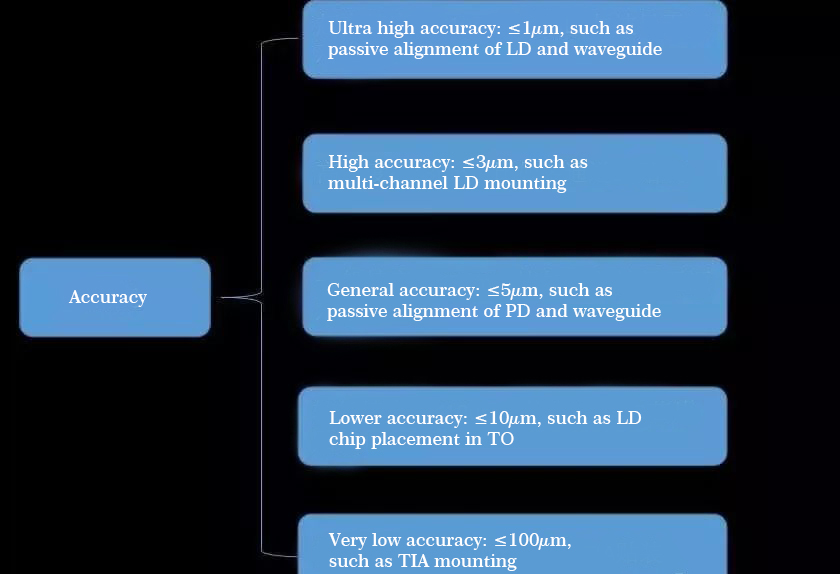

Med allt detta sagt, vad är egentligen en patch? Det verkar aldrig finnas en standardiserad definition. Det kan dock ses från ovanstående exempel att de har en sak gemensamt: enheten används för att placera och fixera placeringskroppen på bäraren med en viss noggrannhet för att uppnå en specifik funktion. (Varför använda utrustning? Jag tror att placeringsprocessen som kan automatiseras kallas en lapp, annars kan den bara kallas manuell bindning.) Utifrån denna gemensamma poäng har jag sammanfattat fyra nyckelelement i en lapp: placeringskroppen, bärare , Fast metod, noggrannhet. Och vilken bärare som används, vilket lod som väljs och vilka noggrannhetskraven är, det beror helt på vilken funktion objektet som ska monteras behöver uppnå.

Här är en titt på de olika möjligheterna som finns i de fyra delarna av patchen:

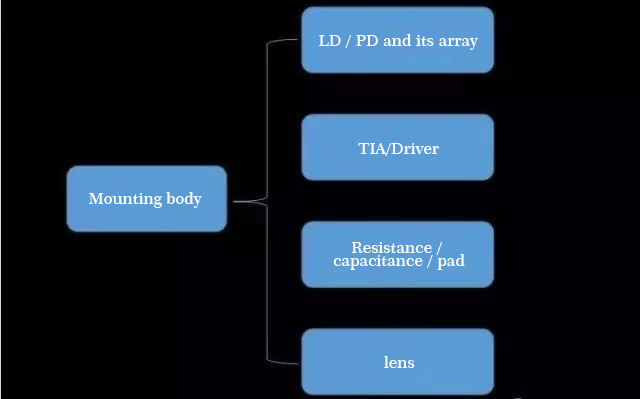

De flesta av fästena är LD- och PD-chips.

TIA / Driver / Resistor / Kondensatorer, såsom placeringskroppar som inte kräver hög noggrannhet, kan bytas ut manuellt istället för stora volymer.

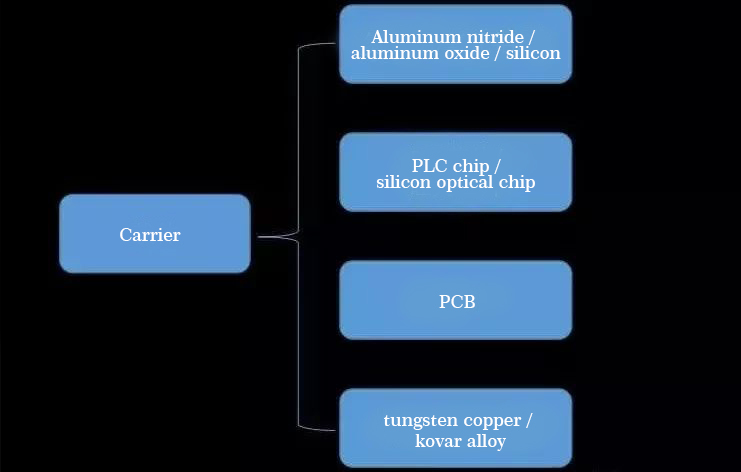

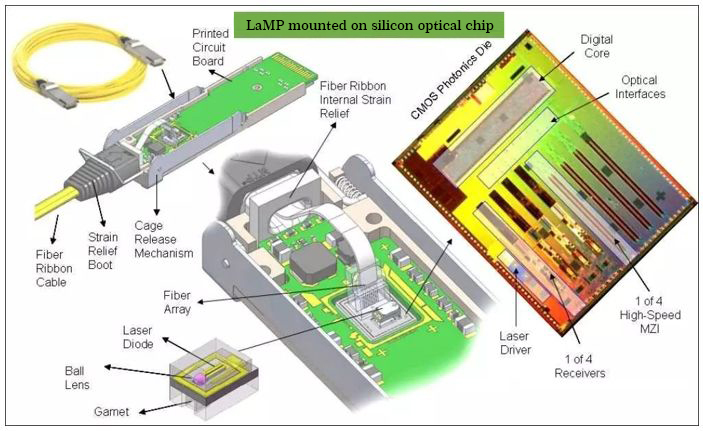

Den mest traditionella bäraren är AIN kylfläns; med utvecklingen av integrerade chips har PLC-chips och optiska kiselchips också blivit vanliga monteringskroppar, såsom kiselljusgitterkopplingschips, som kräver att LAMP monteras på optiska kiselchips; PCB är Vanliga bärare i COB-paket, såsom datakommunikation 100G-SR4 moduler, PD/VSCEL monteras direkt på PCB.

Au80Sn20 legering är ett vanligt LD-monterat eutektiskt lod. Konduktivt lim används ofta för att montera PD. UV-lim fixerad lins är mer lämplig.

Noggrannheten beror på specifik tillämpning;

Där optisk vägkoppling krävs är noggrannhetskravet relativt högt.

Passiv inriktning kräver högre noggrannhet än aktiv koppling.

LD-placering kräver högre noggrannhet än PD-placering,

TIA / motstånd / kondensator behöver ingen precision, bara håll fast den.

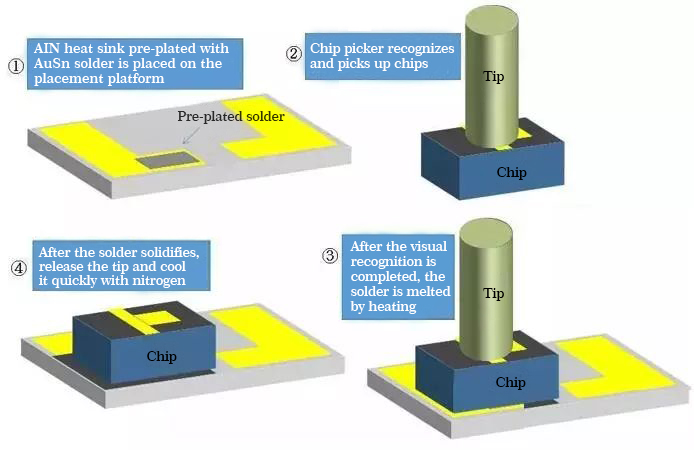

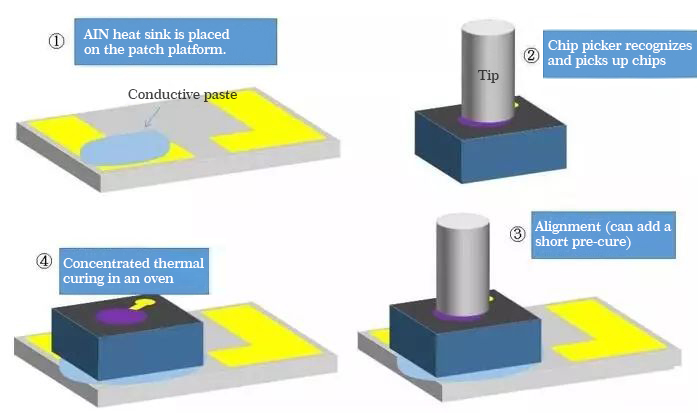

Allmän placeringsprocess

Guld-tenn eutektisk lödplåster

Konduktivt pastaplåster

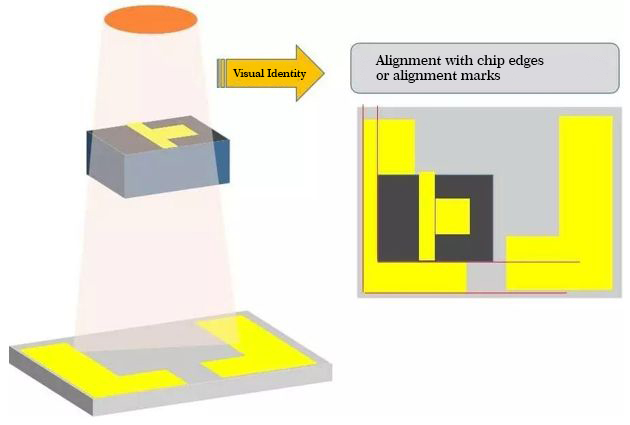

Där noggrannheten inte är hög behöver du bara titta ner på CCD:n för att ta bilder av chipet och substratet samtidigt, och använda justeringsmärken eller chipkanter för att justera

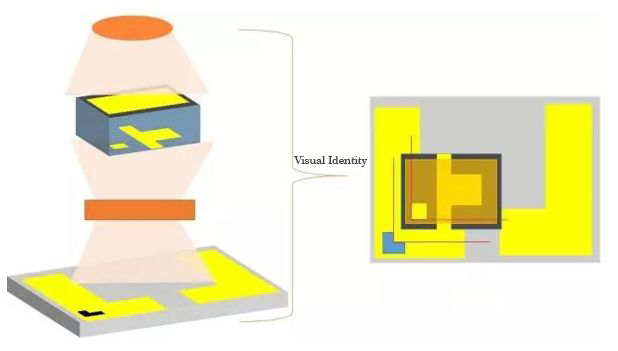

För flip-chip-tillämpningar krävs också flera CCD:er, titta på både botten av chipet och ytan av substratet. Tillämpningar med hög precision kräver också speciella inriktningsmärken.